# Contribution à la conception par la simulation en électronique de puissance: application à l'onduleur basse tension

Cyril Buttay

#### ▶ To cite this version:

Cyril Buttay. Contribution à la conception par la simulation en électronique de puissance : application à l'onduleur basse tension. Sciences de l'ingénieur [physics]. INSA de Lyon, 2004. Français. NNT : . tel-00327164

### HAL Id: tel-00327164 https://theses.hal.science/tel-00327164

Submitted on 7 Oct 2008

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

présentée

#### devant l'Institut National des Sciences Appliquées de Lyon

pour obtenir

#### LE GRADE DE DOCTEUR

ÉCOLE DOCTORALE : ÉLECTRONIQUE ÉLECTROTECHNIQUE AUTOMATIQUE FORMATION DOCTORALE : GÉNIE ÉLECTRIQUE

par

#### **Cyril BUTTAY**

Ingénieur de l'INSA de Lyon

Contribution à la conception par la simulation en électronique de puissance : application à l'onduleur basse tension

Soutenue le : 30 novembre 2004 devant la Commission d'examen

Jury:

M. Patrick AUSTIN, Rapporteur

M. Dominique BERGOGNE, Directeur

M. Jean-Pierre CHANTE

M. François FOREST

M. Cédric Plasse

M. Jean-Luc Schanen, Rapporteur

#### INSTITUT NATIONAL DES SCIENCES APPLIQUEES DE LYON

Directeur: STORCK A.

Professeurs:

AMGHAR Y.

AUDISIO S. PHYSICOCHIMIE INDUSTRIELLE

BABOT D. CONT. NON DESTR. PAR RAYONNEMENTS IONISANTS

GEMPPM\*\* BABOUX J.C.

BALLAND B. PHYSIQUE DE LA MATIERE

BAPTISTE P. PRODUCTIQUE ET INFORMATIQUE DES SYSTEMES MANUFACTURIERS

BARBIER D. PHYSIQUE DE LA MATIERE

BASKURT A. LIRIS LAEPSI\*\*\*\* BASTIDE J.P.

MECANIQUE DES CONTACTS BAYADA G.

LAEPSI\*\* BENADDA B.

BETEMPS M. AUTOMATIQUE INDUSTRIELLE

BIENNIER F. PRODUCTIQUE ET INFORMATIQUE DES SYSTEMES MANUFACTURIERS

BLANCHARD J.M. LAEPSI\*\*\* BOISSE P. LAMCOS

BOISSON C. VIBRATIONS-ACOUSTIQUE BOIVIN M. (Prof. émérite) MECANIQUE DES SOLIDES

BOTTA H. UNITE DE RECHERCHE EN GENIE CIVIL - Développement Urbain BOTTA-ZIMMERMANN M. (Mme) UNITE DE RECHERCHE EN GENIE CIVIL - Développement Urbain

BOULAYE G. (Prof. émérite) INFORMATIQUE

MECANIQUE DES SOLIDES BOYER J.C.

CENTRE DE THERMIQUE DE LYON - Thermique du bâtiment BRAU J.

BREMOND G. PHYSIQUE DE LA MATIERE

BRISSAUD M. GENIE ELECTRIQUE ET FERROELECTRICITE

BRUNET M. MECANIQUE DES SOLIDES

BRUNIE L. INGENIERIE DES SYSTEMES D'INFORMATION

**BUFFIERE J-Y.** GEMPPM\*\*\* CEGELY\* BUREAU J.C. CAMPAGNE J-P. PRISMA GEMPPM\*\*\* CAVAILLE J.Y. CHAMPAGNE J-Y. LMFA

CHANTE J.P. CEGELY\*- Composants de puissance et applications

CHOCAT B. UNITE DE RECHERCHE EN GENIE CIVIL - Hydrologie urbaine

COMBESCURE A. MECANIOUE DES CONTACTS

**COURBON GEMPPM**

UNITE DE RECHERCHE EN GENIE CIVIL - Structures COUSIN M.

DAUMAS F. (Mme) CENTRE DE THERMIQUE DE LYON - Energétique et Thermique

DJERAN-MAIGRE I. UNITE DE RECHERCHE EN GENIE CIVIL

DOUTHEAU A. CHIMIE ORGANIQUE

DUBUY-MASSARD N. **ESCHIL**

DUFOUR R. MECANIQUE DES STRUCTURES PHYSIQUE DE LA MATIERE DUPUY J.C.

EMPTOZ H. RECONNAISSANCE DE FORMES ET VISION ESNOUF C. EYRAUD L. (Prof. émérite) GEMPPM\*\*\* GENIE ELECTRIQUE ET FERROELECTRICITE

FANTOZZI G. GEMPPM\*\*\*

FAVREL J. PRODUCTIQUE ET INFORMATIQUE DES SYSTEMES MANUFACTURIERS

BIOLOGIE FONCTIONNELLE, INSECTES ET INTERACTIONS FAYARD J.M.

MECANIQUE DES SOLIDES FAYET M. (Prof. émérite)

FAZEKAS À. **GEMPPM**

FERRARIS-BESSO G. MECANIQUE DES STRUCTURES MECANIQUE DES CONTACTS FLAMAND L.

FLEURY E. CITI

INGENIERIE DES SYSTEMES D'INFORMATIONS FLORY A.

GEMPPM\*\*\* FOUGERES R. GEMPPM\*\*\* FOUQUET F.

FRECON L. (Prof. émérite) REGROUPEMENT DES ENSEIGNANTS CHERCHEURS ISOLES

GERARD J.F. INGENIERIE DES MATERIAUX POLYMERES GERMAIN P. LAEPSI\*\*\*

GIMENEZ G. CREATIS\*\* GEMPPM\*\*\* GOBIN P.F. (Prof. émérite)

GENIE ELECTRIQUE ET FERROELECTRICITE GONNARD P.

GONTRAND M. PHYSIQUE DE LA MATIERE

GOUTTE R. (Prof. émérite) CREATIS\*\* GEMPPM\*\*\* GOUJON L. LAEPSI\*\*\*\* GOURDON R.

GRANGE G. (Prof. émérite) GENIE ELECTRIQUE ET FERROELECTRICITE

GUENIN G. GEMPPM\*\*\*

GUICHARDANT M. BIOCHIMIE ET PHARMACOLOGIE GUILLOT G. PHYSIQUE DE LA MATIERE

GUINET A. PRODUCTIQUE ET INFORMATIQUE DES SYSTEMES MANUFACTURIERS

GUYADER J.L. VIBRATIONS-ACOUSTIQUE

GENIE ELECTRIQUE ET FERROELECTRICITE GUYOMAR D.

Novembre 2003

HEIBIG A. MATHEMATIQUE APPLIQUEES DE LYON

JACQUET-RICHARDET G. MECANIQUE DES STRUCTURES

JAYET Y. GEMPPM\*\*\*

JOLION J.M. RECONNAISSANCE DE FORMES ET VISION JULLIEN J.F. UNITE DE RECHERCHE EN GENIE CIVIL - Structures JUTARD A. (Prof. émérite) AUTOMATIQUE INDUSTRIELLE

UNITE DE RECHERCHE EN GENIE CIVIL - Géotechnique KASTNER R. KOULOUMDJIAN J. (Prof. émérite) INGENIERIE DES SYSTEMES D'INFORMATION

BIOCHIMIE ET PHARMACOLOGIE LAGARDE M. LALANNE M. (Prof. émérite) MECANIQUE DES STRUCTURES

LALLEMAND A. CENTRE DE THERMIQUE DE LYON - Energétique et thermique CENTRE DE THERMIQUE DE LYON - Energétique et thermique UNITE DE RECHERCHE EN GENIE CIVIL - Géotechnique LALLEMAND M. (Mme) LAREAL P (Prof. émérite)

LAUGIER A. (Prof. émérite) PHYSIQUE DE LA MATIERE BIOCHIMIE ET PHARMACOLOGIE LAUGIER C.

INFORMATIQUE EN IMAGE ET SYSTEMES D'INFORMATION LAURINI R.

LEJEUNE P. UNITE MICROBIOLOGIE ET GENETIQUE

LUBRECHT A. MECANIQUE DES CONTACTS

MASSARD N. INTERACTION COLLABORATIVE TELEFORMATION TELEACTIVITE

PHYSICOCHIMIE INDUSTRIELLE MAZILLE H. (Prof. émérite)

GEMPPM\*\*\* MERLE P. GEMPPM\*\*\* MERLIN J.

INGENIERIE, INFORMATIQUE INDUSTRIELLE MIGNOTTE A. (Mle)

MILLET J.P. PHYSICOCHIMIE INDUSTRIELLE

MIRAMOND M. UNITE DE RECHERCHE EN GENIE CIVIL - Hydrologie urbaine

MOREL R. (Prof. émérite) MECANIQUE DES FLUIDES ET D'ACOUSTIQUES

MOSZKOWICZ P. LAFPSI\*

NARDON P. (Prof. émérite) BIOLOGIE FONCTIONNELLE, INSECTES ET INTERACTIONS

NAVARRO Alain (Prof. émérite) LAEPSI\*\* NELIAS D. LAMCOS

NIEL E. AUTOMATIQUE INDUSTRIELLE

GEMPPM NORMAND B. NORTIER P. DREP CREATIS\*\* ODET C OTTERBEIN M. (Prof. émérite) LAEPSI\*\*\*\*

PARIZET E. VIBRATIONS-ACOUSTIQUE

PASCAULT J.P. INGENIERIE DES MATERIAUX POLYMERES

PAVIC G. VIBRATIONS-ACOUSTIQUE

PECORARO S. **GEMPPM** GEMPPM\*\*\* PELLETIER J.M.

UNITE DE RECHERCHE EN GENIE CIVIL - Matériaux PERA J.

PERRIAT P. GEMPPM\*\* PERRIN J. INTERACTION COLLABORATIVE TELEFORMATION TELEACTIVITE

PINARD P. (Prof. émérite) PHYSIQUE DE LA MATIERE

INGENIERIE DES SYSTEMES D'INFORMATION PINON J.M.

PONCET A. PHYSIQUE DE LA MATIERE

POUSIN J. MODELISATION MATHEMATIQUE ET CALCUL SCIENTIFIQUE PREVOT P. INTERACTION COLLABORATIVE TELEFORMATION TELEACTIVITE PROST R.

RAYNAUD M. CENTRE DE THERMIQUE DE LYON - Transferts Interfaces et Matériaux

REDARCE H. AUTOMATIQUE INDUSTRIELLE

CEGELY\* RETIF J-M.

UNITE DE RECHERCHE EN GENIE CIVIL - Structures REYNOUARD J.M.

RICHARD C. **LGEF**

RIGAL J.F. MECANIQUE DES SOLIDES RIEUTORD E. (Prof. émérite) MECANIQUE DES FLUIDES

ROBERT-BAUDOUY J. (Mme) (Prof. émérite) GENETIQUE MOLECULAIRE DES MICROORGANISMES

GEMPPM\*\*\* ROUBY D.

CENTRE DE THERMIQUE DE LYON – Thermique de l'Habitat ROUX J.J.

RUBEL P. INGENIERIE DES SYSTEMES D'INFORMATION

SACADURA J.F. CENTRE DE THERMIQUE DE LYON - Transferts Interfaces et Matériaux

SAUTEREAU H. INGENIERIE DES MATERIAUX POLYMERES

SCAVARDA S. (Prof. émérite) AUTOMATIQUE INDUSTRIELLE SOUIFI A. PHYSIQUE DE LA MATIERE INGENIERIE INFORMATIQUE INDUSTRIELLE SOUROUILLE J.L.

THOMASSET D. AUTOMATIQUE INDUSTRIELLE

THUDEROZ C. ESCHIL – Equipe Sciences Humaines de l'Insa de Lyon

UBEDA S. CENTRE D'INNOV. EN TELECOM ET INTEGRATION DE SERVICES

VELEX P. MECANIQUE DES CONTACTS

VERMANDE P. (Prof émérite) LAEPSI GEMPPM\*\*\* VIGIER G. GEMPPM\*\*\* VINCENT A. VRAY D. CREATIS\*\*

VUILLERMOZ P.L. (Prof. émérite) PHYSIQUE DE LA MATIERE

Directeurs de recherche C.N.R.S.:

BERTHIER Y. MECANIQUE DES CONTACTS

UNITE MICROBIOLOGIE ET GENETIQUE CONDEMINE G.

UNITE MICROBIOLOGIE ET GENETIQUE **COTTE-PATAT N.** (Mme) ESCUDIE D. (Mme) CENTRE DE THERMIQUE DE LYON

FRANCIOSI P. GEMPPM\*\*\*

MANDRAND M.A. (Mme) POUSIN G. UNITE MICROBIOLOGIE ET GENETIQUE BIOLOGIE ET PHARMACOLOGIE

ROCHE A. INGENIERIE DES MATERIAUX POLYMERES

GEMPPM\*\*\* SEGUELA A. VERGNE P. LaMcos

Directeurs de recherche I.N.R.A. : FEBVAY G. GRENIER S. BIOLOGIE FONCTIONNELLE, INSECTES ET INTERACTIONS BIOLOGIE FONCTIONNELLE, INSECTES ET INTERACTIONS RAHBE Y. BIOLOGIE FONCTIONNELLE, INSECTES ET INTERACTIONS

Directeurs de recherche I.N.S.E.R.M.:

KOBAYASHI T. PLM

PRIGENT A.F. (Mme) BIOLOGIE ET PHARMACOLOGIE

CREATIS\*\* MAGNIN I. (Mme)

\* CEGELY CENTRE DE GENIE ELECTRIQUE DE LYON

\*\* CREATIS CENTRE DE RECHERCHE ET D'APPLICATIONS EN TRAITEMENT DE L'IMAGE ET DU SIGNAL

\*\*\*\*GEMPPM GROUPE D'ETUDE METALLURGIE PHYSIQUE ET PHYSIQUE DES MATERIAUX

\*\*\*\*\*LAEPSI LABORATOIRE D'ANALYSE ENVIRONNEMENTALE DES PROCEDES ET SYSTEMES INDUSTRIELS

| SIGLE   | ECOLE DOCTORALE                                   | NOM ET COORDONNEES DU RESPONSABLE                                 |

|---------|---------------------------------------------------|-------------------------------------------------------------------|

|         |                                                   |                                                                   |

|         | CHIMIE DE LYON                                    | M. Denis SINOU                                                    |

|         | <u> </u>                                          | Université Claude Bernard Lyon 1                                  |

|         |                                                   | Lab Synthèse Asymétrique UMR UCB/CNRS 5622                        |

|         |                                                   | Bât 308                                                           |

|         |                                                   | 2 <sup>ème</sup> étage                                            |

|         |                                                   | 43 bd du 11 novembre 1918                                         |

|         |                                                   | 69622 VILLEURBANNE Cedex                                          |

|         |                                                   | Tél: 04.72.44.81.83                                               |

|         |                                                   | sinou@univ-lyon1.fr                                               |

|         | ECONOMIE, ESPACE ET MODELISATION                  | M. Alain BONNAFOUS                                                |

| E2MC    | DES COMPORTEMENTS                                 | Université Lyon 2                                                 |

|         |                                                   | 14 avenue Berthelot<br>MRASH                                      |

|         |                                                   | Laboratoire d'Economie des Transports                             |

|         |                                                   | 69363 LYON Cedex 07                                               |

|         |                                                   | Tél: 04.78.69.72.76                                               |

|         |                                                   | Alain.Bonnafous@mrash.fr                                          |

|         | ELECTRONIQUE, ELECTROTECHNIQUE,                   | M. Daniel BARBIER                                                 |

| E.E.A.  | AUTOMATIQUE                                       | INSA DE LYON                                                      |

|         |                                                   | Laboratoire Physique de la Matière                                |

|         |                                                   | Bâtiment Blaise Pascal                                            |

|         |                                                   | 69621 VILLEURBANNE Cedex                                          |

|         |                                                   | Tél: 04.72.43.64.43                                               |

|         |                                                   | <u>Daniel.Barbier@insa-lyon.fr</u>                                |

|         | EVOLUTION, ECOSYSTEME,                            | M. Jean-Pierre FLANDROIS                                          |

| E2M2    | MICROBIOLOGIE, MODELISATION                       | UMR 5558 Biométrie et Biologie Evolutive                          |

|         | http://biomserv.univ-lyon1.fr/E2M2                | Equipe Dynamique des Populations Bactériennes                     |

|         |                                                   | Faculté de Médecine Lyon-Sud Laboratoire de Bactériologie BP      |

|         |                                                   | 1269600 OULLINS                                                   |

|         |                                                   | Tél: 04.78.86.31.50                                               |

|         | THEODIA MICHE EM INECDIA MICH                     | Jean-Pierre.Flandrois@biomserv.univ-lyon1.fr M. Lionel BRUNIE     |

| EDIIS   | INFORMATIQUE ET INFORMATION POUR LA SOCIETE       | INSA DE LYON                                                      |

| EDIIS   | http://www.insa-lyon.fr/ediis                     | EDIIS                                                             |

|         | intp://www.msa-ryon.m/cdms                        | Bâtiment Blaise Pascal                                            |

|         |                                                   | 69621 VILLEURBANNE Cedex                                          |

|         |                                                   | Tél: 04.72.43.60.55                                               |

|         |                                                   | lbrunie@if.insa-lyon.fr                                           |

|         | INTERDISCIPLINAIRE SCIENCES-SANTE                 | M. Alain Jean COZZONE                                             |

| EDISS   | http://www.ibcp.fr/ediss                          | IBCP (UCBL1)                                                      |

|         |                                                   | 7 passage du Vercors                                              |

|         |                                                   | 69367 LYON Cedex 07                                               |

|         |                                                   | Tél: 04.72.72.26.75                                               |

|         | MATERIAUX DE LYON                                 | cozzone@ibcp.fr  M. Jacques JOSEPH                                |

|         | http://www.ec-lyon.fr/sites/edml                  | Ecole Centrale de Lyon                                            |

|         | intp.//www.co.ryon.n/sites/cumi                   | Bât F7 Lab. Sciences et Techniques des Matériaux et des           |

|         |                                                   | Surfaces                                                          |

|         |                                                   | 36 Avenue Guy de Collongue BP 163                                 |

|         |                                                   | 69131 ECULLY Cedex                                                |

|         |                                                   | Tél: 04.72.18.62.51                                               |

| <u></u> |                                                   | Jacques.Joseph@ec-lyon.fr                                         |

|         | MATHEMATIQUES ET INFORMATIQUE                     | M. Franck WAGNER                                                  |

| Math IF | <u>FONDAMENTALE</u>                               | Université Claude Bernard Lyon l                                  |

|         | http://www.ens-lyon.fr/MathIS                     | Institut Girard Desargues                                         |

|         |                                                   | UMR 5028 MATHEMATIQUES                                            |

|         |                                                   | Bâtiment Doyen Jean Braconnier                                    |

|         |                                                   | Bureau 101 Bis, 1 <sup>er</sup> étage<br>69622 VILLEURBANNE Cedex |

|         |                                                   | Tél: 04.72.43.27.86                                               |

|         |                                                   | wagner@desargues.univ-lyon1.fr                                    |

|         | MECANIQUE, ENERGETIQUE, GENIE                     | M. François SIDOROFF                                              |

| MEGA    | CIVIL, ACOUSTIQUE  CIVIL ACOUSTIQUE               | Ecole Centrale de Lyon                                            |

|         | http://www.lmfa.ec-lyon.fr/autres/MEGA/index.html | Lab. Tribologie et Dynamique des Systêmes Bât G8                  |

|         |                                                   | 36 avenue Guy de Collongue                                        |

|         |                                                   | BP 163                                                            |

|         |                                                   | 69131 ECULLY Cedex                                                |

|         |                                                   | Tél :04.72.18.62.14                                               |

|         |                                                   | Francois.Sidoroff@ec-lyon.fr                                      |

|         |                                                   |                                                                   |

# Table des matières

| Re | emer | ciemer       | nts                                                      |   | 3  |

|----|------|--------------|----------------------------------------------------------|---|----|

| In | trod | uction       |                                                          |   | 5  |

| 1  | Le N | <b>10SFE</b> | T de puissance basse tension                             |   | 13 |

|    | 1.1  | Fonct        | tionnement des transistors MOSFET                        |   | 13 |

|    |      | 1.1.1        | La structure MOS                                         |   | 13 |

|    |      | 1.1.2        | Le MOSFET latéral                                        |   | 15 |

|    |      | 1.1.3        | Le MOSFET vertical                                       |   | 17 |

|    |      | 1.1.4        | Comportement statique                                    |   | 18 |

|    |      | 1.1.5        | Comportement dynamique                                   |   | 21 |

|    |      |              | 1.1.5.1 Capacités parasites                              |   |    |

|    |      |              | 1.1.5.2 Éléments inductifs                               |   | 23 |

|    |      |              | 1.1.5.3 Diode intrinsèque                                |   |    |

|    | 1.2  | Spéci        | ficités des applications basse tension, fort courant     |   |    |

|    |      | 1.2.1        | Compromis tenue en tension/résistance à l'état passant . |   |    |

|    |      |              | 1.2.1.1 Routage en bande (strip MOS)                     |   |    |

|    |      |              | 1.2.1.2 Le UDMOS ou <i>trench</i> MOSFET                 |   |    |

|    |      | 1.2.2        | Utilisation de la diode interne dans un Onduleur         |   | 30 |

|    |      | 1.2.3        | Influence de la température sur le comportement du tran  | - |    |

|    |      |              | sistor                                                   |   |    |

|    |      |              | 1.2.3.1 Modification de la caractéristique statique      |   |    |

|    |      |              | 1.2.3.2 Modification du comportement dynamique           |   |    |

|    |      | 1.2.4        | Limitations du boîtier                                   |   |    |

|    | 1.3  |              | Elisation                                                |   |    |

|    |      | 1.3.1        | Modèle électrique                                        |   |    |

|    |      |              | 1.3.1.1 Modèle statique                                  |   |    |

|    |      |              | 1.3.1.2 Capacités                                        |   |    |

|    |      |              | 1.3.1.3 Diode                                            |   |    |

|    |      |              | 1.3.1.4 Tenue en avalanche                               |   |    |

|    |      | 1.3.2        | Modélisation électrothermique                            |   |    |

|    |      |              | 1.3.2.1 Modèle thermique                                 |   | 45 |

|   |      | 1.3.3     | Mise en œuvre du modèle Pspice                           | <br>49 |

|---|------|-----------|----------------------------------------------------------|--------|

|   |      |           | 1.3.3.1 Les <i>ABM</i>                                   |        |

|   |      |           | 1.3.3.2 Modèle électrique                                | <br>50 |

|   |      |           | 1.3.3.3 Les problèmes de convergence                     | <br>50 |

|   | 1.4  | Concl     | lusion                                                   | <br>51 |

| 2 | Circ | cuit et c | câblage                                                  | 53     |

|   | 2.1  |           | rtance de la prise en compte du câblage                  |        |

|   |      | 2.1.1     |                                                          |        |

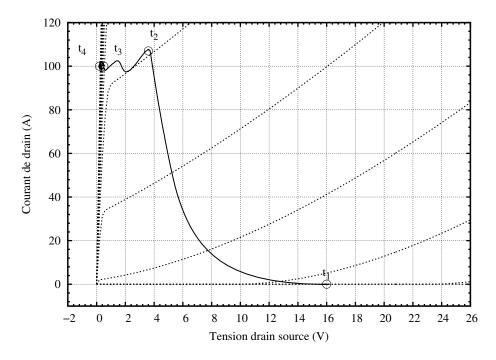

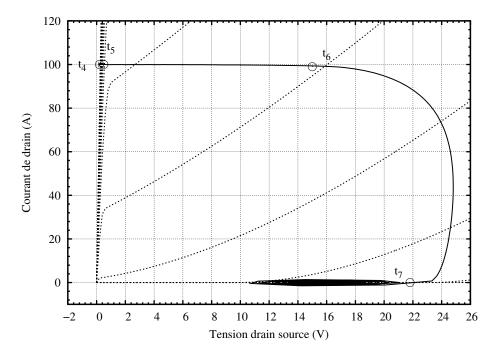

|   |      | 2.1.2     | Déroulement d'un cycle de commutation                    |        |

|   |      |           | 2.1.2.1 Fermeture du MOSFET                              |        |

|   |      |           | 2.1.2.2 Ouverture du MOSFET                              |        |

|   |      | 2.1.3     |                                                          |        |

|   |      |           | 2.1.3.1 Formes d'ondes                                   |        |

|   |      |           | 2.1.3.2 Pertes                                           |        |

|   |      |           | 2.1.3.3 Récapitulatif                                    |        |

|   | 2.2  | Modé      | lisation du câblage                                      |        |

|   |      | 2.2.1     | Méthodes                                                 |        |

|   |      |           | 2.2.1.1 Définition de l'inductance                       | <br>77 |

|   |      |           | 2.2.1.2 Notion d'inductance partielle                    |        |

|   |      |           | 2.2.1.3 Extraction des paramètres d'une géométrie        |        |

|   |      |           | 2.2.1.4 Calcul des capacités                             |        |

|   |      | 2.2.2     | Outils                                                   |        |

|   |      |           | 2.2.2.1 Méthodologie de description                      |        |

|   |      |           | 2.2.2.2 Modélisation <i>Pspice</i>                       |        |

|   | 2.3  | Concl     | lusion                                                   |        |

| 3 | Car  | actéris   | ation et validation expérimentale                        | 87     |

| Ü | 3.1  |           | ns de mesure                                             |        |

|   | 0.1  | 3.1.1     |                                                          |        |

|   |      | 0.1.1     | 3.1.1.1 Instruments de mesure utilisés                   |        |

|   |      |           | 3.1.1.2 Conditions de mesure                             |        |

|   |      |           | 3.1.1.3 Composant étudié                                 |        |

|   |      | 3.1.2     | Mesures calorimétriques                                  |        |

|   | 3.2  |           | térisation                                               |        |

|   | 0.2  | 3.2.1     | MOSFET                                                   |        |

|   |      | 0.2.1     | 3.2.1.1 Caractéristique statique                         |        |

|   |      |           | 3.2.1.2 Caractéristique dynamique                        |        |

|   |      |           | 3.2.1.3 Caractéristique statique de la diode intrinsèque |        |

|   |      |           | 3.2.1.4 Fonctionnement en avalanche                      |        |

|   |      |           | 3.2.1.5 Récapitulatif des paramètres identifiés          |        |

|   |      | 3.2.2     | Câblage                                                  |        |

|   |      |           |                                                          |        |

| TARI | $\mathbf{E}$ D | )FS | MΑ | TIER | FS |

|------|----------------|-----|----|------|----|

| ì | v |

|---|---|

|   |   |

|   |   |

|    |      | 3.2.2.1 Modélisation inductive et résistive                | 121 |

|----|------|------------------------------------------------------------|-----|

|    |      | 3.2.2.2 Modélisation capacitive                            |     |

|    | 3.3  | Validation                                                 |     |

|    |      | 3.3.1 Mesures calorimétriques                              |     |

|    |      | 3.3.1.1 Dispositif de validation                           |     |

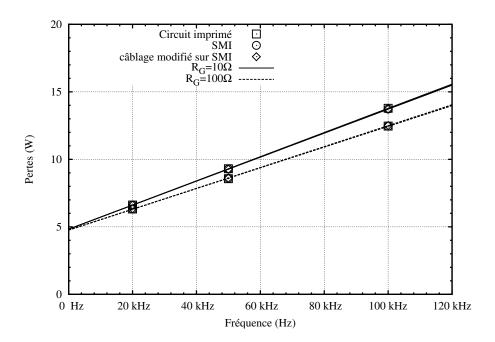

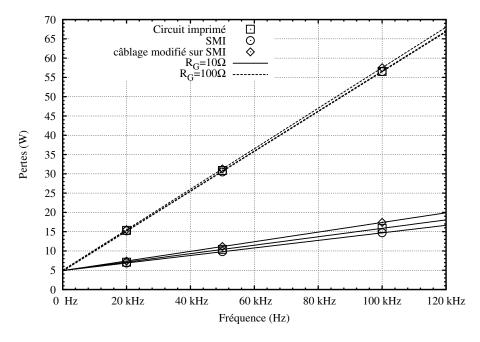

|    |      | 3.3.1.2 Résultats                                          |     |

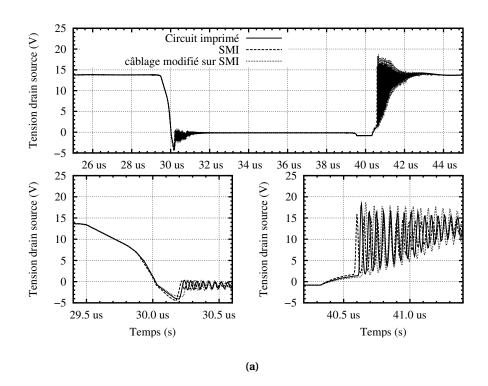

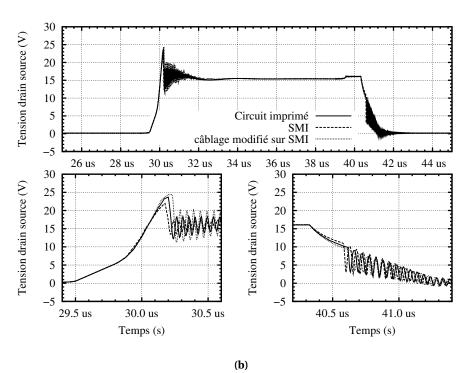

|    |      | 3.3.2 Mesures temporelles                                  | 135 |

|    |      | 3.3.3 Validation du modèle électrothermique de l'avalanche | 140 |

|    | 3.4  | Conclusion                                                 | 143 |

| 4  | Exp  | oitation de l'outil de simulation                          | 145 |

|    | 4.1  | Minimisation des pertes                                    | 145 |

|    |      | 4.1.1 Influence du routage                                 |     |

|    |      | 4.1.1.1 Modélisation du câblage                            |     |

|    |      | 4.1.1.2 Résultats de simulation                            | 149 |

|    |      | 4.1.2 Choix des paramètres du <i>driver</i>                | 152 |

|    | 4.2  | Mise en parallèle                                          | 159 |

|    |      | 4.2.1 Présentation de la structure                         | 160 |

|    |      | 4.2.2 Équilibrage entre transistors                        | 162 |

|    |      | 4.2.2.1 Équilibrage statique                               | 162 |

|    |      | 4.2.2.2 Équilibrage dynamique                              |     |

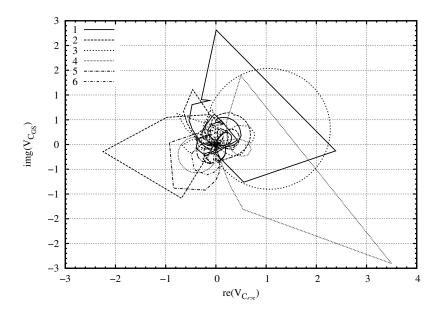

|    |      | 4.2.3 Stabilité de l'association                           | 178 |

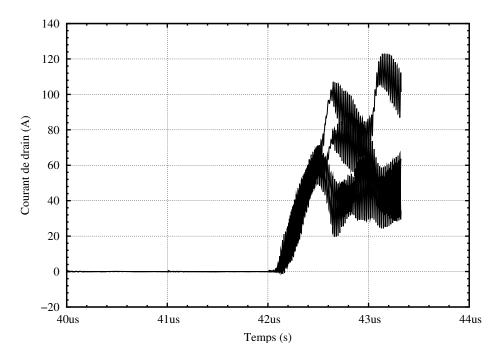

|    |      | 4.2.4 Comportement en régime d'avalanche                   |     |

|    |      | 4.2.4.1 Modélisation                                       |     |

|    |      | 4.2.4.2 Résultats de simulation                            |     |

|    | 4.3  | Conclusions                                                | 188 |

| Co | nclu | sion générale                                              | 191 |

| A  | Mod  | èle Pspice du MOSFET de puissance                          | 203 |

| В  | Mod  | èles de câblage                                            | 207 |

| C  | Moy  | ens expérimentaux                                          | 209 |

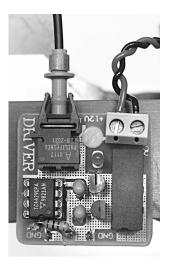

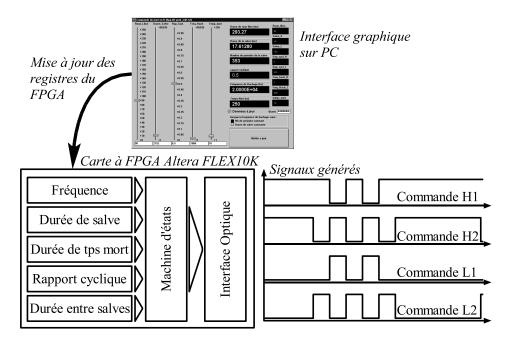

|    | C.1  | Génération des signaux de commande                         | 209 |

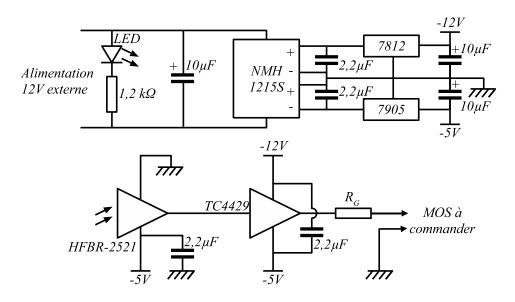

|    | C.2  | Driver isolé                                               | 210 |

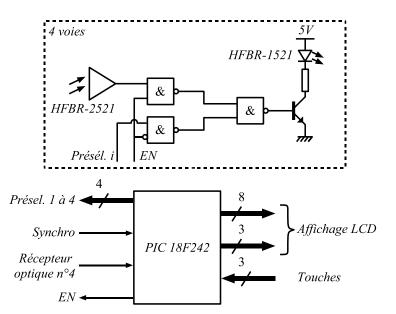

|    | C.3  | Porte optique                                              | 211 |

# Liste des symboles

Paramètre empirique du modèle de diode, page 44  $\alpha$ Coefficient d'évolution de la tension d'avalanche avec la température  $(VK^{-1})$ , β page 44 Permitivité de l'oxyde de silicium  $(F.m^{-1})$ , page 22  $\epsilon_{ox}$ Permitivité du silicium  $(1,04.10^{-8}F.m^{-1})$ , page 14  $\epsilon_{Si}$ Paramètre empirique de la variation de longueur de canal  $(V^{-1})$ , page 40 λ Perméabilité du vide  $(4\pi.10^{-7}N.A^{-2})$ , page 78  $\mu_0$ Mobilité de surface des électrons dans une couche d'accumulation ( $cm.s^{-1}.V^{-1}$ ),  $\mu_{ns_a}$ page 19 Mobilité de surface des électrons ( $cm^2.s^{-1}.V^{-1}$ ), page 15  $\mu_{ns}$  $\Phi_P$ Potentiel de surface en régime d'inversion (V), page 14 Flux magnétique à travers la surface définie par le circuit *j* créé par le courant  $\Phi_{i\,i}$ parcourant le circuit i (Wb), page 77  $\Phi_{MS}$ Potentiel Métal–Semiconducteur (V), page 14  $\Phi_S$ Potentiel de surface (V), page 14 Densité  $(g.m^{-3})$ , page 46 ρ Paramètre empirique d'évolution de la tension de seuil $(V^{-1})$ , page 41  $\sigma$ Coefficient de proportionnalité entre le courant de trous et la charge stockée  $\tau_D$ (s), page 44  $\theta$ Paramètre empirique de la modulation de mobilité dans le canal  $(V^{-1})$ , page 40  $\vec{A}_i$ Potentiel vecteur magnétique ( $Wb.m^{-1}$ ), page 78  $\vec{B}$ Champ magnétique (T), page 77 Surfaces de grille et de drain en regard  $(m^2)$ , page 23  $A_{GD}$  $A_{MOS}$ Surface du transistor  $(m^2)$ , page 46 Capacité calorifique massique  $(J.g^{-1}.K^{-1})$ , page 46 c $C_{DS}$ Capacité drain-source (C), page 22 Capacité grille-drain formée par la ZCE (F), page 22  $C_{GDi}$ Capacité grille-drain (C), page 22  $C_{GD}$ Capacite grille-source (F), page 23  $C_{GS}$ Capacité d'entrée, drain et source court-circuités (F), page 23  $C_{iss}$  $C_{oss}$ Capacité de sortie, grille et source court-circuités (F), page 23  $C_{oxD}$ Capacité grille-drain formée la couche d'oxyde (F), page 22

Capacité grille-métallisation de source (C), page 22

$C_{oxm}$

$R_a$

```

C_{oxN^+}

Capacité grille-zone N+(C), page 22

C_{oxP}

Capacité grille-zone P (C), page 22

Capacité de l'oxyde (F), page 14

C_{ox}

Capacité de contre-réaction (F), page 23

C_{rss}

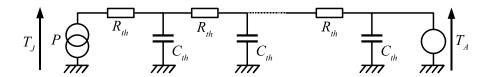

Capacité thermique (J.K^{-1}), page 48

C_{TH}

D

Coefficient de diffusion ambipolaire (cm.s^{-1}), page 42

E

Énergie dissipée (J), page 94

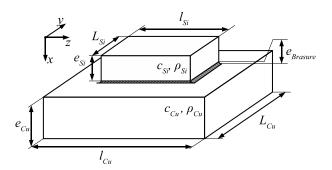

e<sub>Brasure</sub> épaisseur de la brasure entre puce et semelle(m), page 46

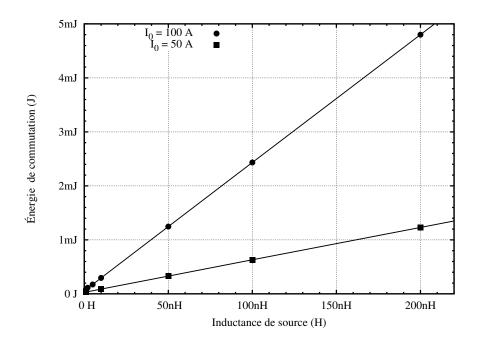

E_{commut.} Énergie de commutation (W), page 126

épaisseur de la semelle de cuivre (m), page 46

e_{Cu}

Épaisseur de la zone de charge d'espace formant C_{GDj} (m), page 23

e_{GDj}

e_{ox}

Épaisseur de l'oxyde de silicium (m), page 22

épaisseur du pavé de silicium (m), page 46

e_{Si}

Fréquence de découpage du convertisseur (Hz), page 126

F

h

Pas de discrétisation (m), page 48

I_D

Courant de drain (A), page 16

i_n

Courant d'électrons (A), page 43

Courant de trous (A), page 43

i_p

Courant de drain en régime de saturation (A), page 16

I_{D,sat}

K

Conductivité thermique (W.m^{-1}.K^{-1}), page 46

k

Facteur empirique, page 19

« Transconductance » du MOSFET (A.V^{-2}), page 34

K_{v}

Facteur de la loi racine, page 47

k_{therm}

« Transconductance » en régime linéaire (A.V^{-2}), page 40

Kp_{lin}

« Transconductance » en régime de saturation (A.V^{-2}), page 40

Kp_{sat}

L

Self inductance (H), page 77

L_{Cu}

épaisseur de la semelle de cuivre (m), page 46

épaisseur du de la semelle de cuivre (m), page 46

l_{Cu}

épaisseur du pavé de silicium (m), page 46

L_{Si}

épaisseur du pavé de silicium (m), page 46

l_{Si}

M_{ij}

Mutuelle inductance entre les circuits i et j (H), page 77

Concentration d'électrons (cm^{-3}), page 14

n

Dopage P (cm^{-3}), page 14

N_A

Concentration intrinsèque (cm^{-3}), page 14

n_i

P

Puissance (W), page 46

P

Puissance dissipée (W), page 47

Pertes en conduction (W), page 126

P_{cond}.

Charge électronique (1,602.10^{-19}C), page 14

q

Charge d'interface oxyde-semiconducteur(C), page 14

Q_0

Charge participant à la conduction dans le canal d'un MOSFET (C), page 15

Q_n

R_{\nu}

Résistance de la couche épitaxiée (\Omega), page 19

```

Résistance de la zone d'accumulation située sous la grille  $(\Omega)$ , page 19

| $R_D$         | Résistance de drain $(\Omega)$ , page 19                                         |

|---------------|----------------------------------------------------------------------------------|

| $R_S$         | Résistance de source $(\Omega)$ , page 19                                        |

| $R_{BR}$      | Résistance dynamique durant l'avalanche ( $\Omega$ ), page 44                    |

| $R_{ch}$      | Résistance du canal ( $\Omega$ ), page 15                                        |

| $R_{JFET}$    | Résistance occasionnée par l'effet $JFET$ parasite $(\Omega)$ , page 19          |

| $R_{TH}$      | Résistance thermique ( $K.W^{-1}$ ), page 48                                     |

| T             | Température absolue(K), page 34                                                  |

| $T_a$         | Température ambiante (K), page 46                                                |

| $t_{d_{off}}$ | Délai entre l'application de la tension de commande et l'ouverture du transistor |

| -3,7          | (s), page 28                                                                     |

| $t_{d_{on}}$  | Délai entre l'application de la tension de commande et la fermeture du transis-  |

|               | tor (s), page 28                                                                 |

| $U_T$         | Unité thermodynamique, égale à $\frac{kT}{q}$ (V), page 14                       |

| $V_T$         | Tension de seuil à $V_{DS}$ nul $(V)$ , page 41                                  |

| $V_{BR_0}$    | Tension d'avalanche à courant nul et 0°C ( $V$ ), page 44                        |

| $V_{BR}$      | Tension de claquage du transistor $(V)$ , page 20                                |

| $V_{FB}$      | Tension de bande plate (Flat Band) (V), page 14                                  |

| $V_{GB}$      | Tension Bulk (substrat)–Grille (V), page 14                                      |

| W             | Largeur du canal (m), page 15                                                    |

| $w_C$         | Extension de la zone de charge d'espace (m), page 43                             |

| $W_{JFET}$    | Largeur de la zone de charge d'espace du JFET parasite (m), page 20              |

| $R_{DS_{on}}$ | Résistance totale en régime linéaire $(\Omega)$ , page 19                        |

| $V_{th}$      | Tension de seuil du MOSFET $(V)$ , page 14                                       |

|               |                                                                                  |

La lettre s en exposant définit une valeur surfacique

Puisque ces mystères me dépassent, feignons d'en être les organisateurs.

JEAN COCTEAU, *Les Mariés de la tour Eiffel.*

### Remerciements

Je tiens à remercier chaleureusement les personnes de *Valeo Systèmes Électriques* qui ont œuvré pour le financement de cette étude. Ne les connaissant certainement pas toutes, mes remerciements iront à Cédric Plasse – manager recherche et développement électronique – pour sa volonté sans faille de faire coopérer l'industrie et la recherche. À charge pour lui de transmettre ma gratitude à qui de droit...

Les membres du jury, qui ont accepté de leur plein gré la lourde charge d'évaluer ce travail méritent également mes sincères remerciements. Veuillez accepter, messieurs patrick AUSTIN, François FOREST et jean-Luc SCHANEN mes plus plates excuses pour la longueur du manuscrit.

Ce travail n'aurait sans doute pas pu aboutir sans le soutien de Hervé MOREL, directeur du CEGELY-INSA. Je lui serai encore longtemps reconnaissant de ses judicieux conseils. Merci également à Jean-Pierre Chante – directeur en second de cette thèse – de m'avoir accueilli au début de cette thèse dans son laboratoire. Dominique Bergogne, enfin, directeur de cette thèse, doit être remercié ici de la liberté dont il a su me laisser jouir.

Remerciements encore à toutes les personnes avec qui j'ai pu travailler ou que j'ai pu côtoyer durant ces trois années: Philippe MASSON, Gaël BLONDEL, Guillaume LACAMOIRE, Luc KOBYLANSKI, mais également toutes les personnes du pôle de recherche et développement électronique de *Valeo Systèmes Électriques*, à Créteil. Au CEGELY, mes sincères remerciements iront à tout le monde indistinctement (ce qui m'évite d'oublier qui que ce soit) pour l'accueil dont j'ai pu profiter. Bonne chance aux doctorants à venir. Bonne chance enfin à celles et ceux – dont je fais désormais partie – maintenant diplômés, qui espèrent un jour obtenir un poste.

#### L'électronique dans l'automobile

#### Une présence de plus en plus marquée

Le développement de l'électronique dans les automobiles se fait selon deux axes distincts: d'un côté il autorise de nouvelles fonctions (ABS, système d'aide à la navigation...), et de l'autre, l'électrification d'actionneurs mécaniques (climatisation, assistance de direction...) donne une plus grande souplesse de conception. Une grande partie des actionneurs auxiliaires est désormais électrique [Lar02]. Il est ainsi possible d'obtenir une commande plus précise et plus souple qu'avec un actionneur qui tire son énergie du moteur thermique (cas des injecteurs ou de l'allumage). D'autre part, l'implantation des actionneurs électriques n'étant plus tributaire d'une liaison mécanique (courroie, axe...), elle est plus aisée.

Tous ces avantages expliquent le recours massif aux solutions électriques, ce qui fait que dès à présent le coût du système électrique d'une automobile moyenne est plus élevé que celui de sa chaîne de traction (moteur et transmission) [Kas01]. Et l'évolution prévisible [Dos01] devrait amener à accroître encore la part de l'électricité dans le coût total: cantonnée pour l'instant aux fonctions auxiliaires ou à l'assistance des fonctions principales (ABS, direction assistée...), l'électrification devrait à terme atteindre les fonctions principales elles-même. Freinage et direction entièrement électriques sont les applications les plus marquantes du concept marketing *x-by-wire* (x-par-fil, x pouvant être n'importe quelle fonction ou organe du véhicule).

Il est alors normal que les constructeurs soient très attentifs aux évolutions des systèmes électriques. Un des exemples frappants est celui du passage de la tension de bord de 12 à 42 V [Kas01]. L'augmentation de cette tension (qui est déjà passée de 6 à 12 V au cours des années 50) semble inéluctable à plus ou moins long terme afin de pouvoir satisfaire une consommation électrique de plus en plus importante, et la valeur de 42 V constitue une limite haute audelà de laquelle certains choix techniques doivent être remis en cause (au niveau des sécurités notamment). Au départ enthousiastes, de nombreux constructeurs

sont maintenant plus circonspects, voire opposés à cette évolution devant les coûts très élevés qu'elle entraîne [Fed04].

#### La motorisation électrique

Les systèmes auxquels nous allons nous intéresser dans ce mémoire sont notamment destinés à l'application *alterno-démarreur*, qui constitue le premier pas vers le véhicule hybride, à moteurs thermique et électrique.

La motorisation thermique présente sur son concurrent électrique un avantage de « poids » : la densité énergétique des carburants est plus de 200 fois supérieure à celle des batteries  $^1$  (42500 kJ/kg pour le diesel contre 180 kJ/kg pour une batterie NiCd, et encore deux fois moins pour un accumulateur au plomb). Le stockage énergétique constitue le principal frein au développement du véhicule électrique.

Cependant, le rendement de conversion d'un moteur thermique, déjà relativement faible au point de fonctionnement optimal (environ 40 %), chute à 15 % si l'on considère un cycle de conduite complet (cycle comprenant, entre autres, accélérations, freinages et arrêt du véhicule). Sur ce point, le moteur électrique possède bien des avantages (absence de consomation au point mort, rendement de conversion électro-mécanique élevé...). D'autre part, la motorisation électrique autorise plus de souplesse dans la conception de la chaîne de traction du véhicule: on peut implanter directement la motorisation dans les roues (on supprime ainsi les organes de transmission mécanique). il est également possible de supprimer la boîte de vitesse en utilisant un moteur capable de fournir le couple nécessaire sur une large plage de vitesses.

Une des voies explorées pour utiliser au mieux les moteurs thermiques et réduire leurs émissions polluantes passe donc par l'association avec un moteur électrique. Cette motorisation « hybride » permet ainsi de conjuguer la forte densité énergétique des carburants pétroliers avec la souplesse d'emploi du moteur électrique.

#### Architectures d'hybridation

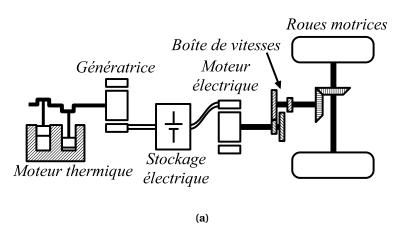

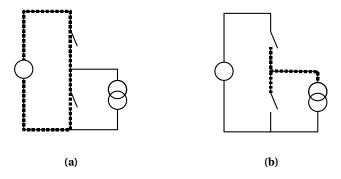

La première architecture de motorisation hybride qui peut venir à l'esprit est constituée d'un moteur thermique relié à une génératrice pour effectuer la conversion carburant/électricité, puis d'un moteur électrique assurant la conversion électromécanique. Elle est appelée hybride « série » et est représentée figure 1(a). Ses principaux avantages sont :

le moteur thermique, découplé de l'entraînement, fonctionne à son régime optimal. Son rendement de conversion est maximal, et ses émissions polluantes minimales;

<sup>1.</sup> Source : Mémoire de thèse de Luc Kobylanski, en cours de rédaction

Fig. 1 – Principe des véhicules hybrides : hybrides « série » (a) et « parallèle » (b).

peu de liaisons mécaniques. On peut implanter le moteur thermique et la génératrice n'importe où dans le véhicule, puisque la liaison avec le moteur électrique se fait par des câbles électriques;

la caractéristique couple/vitesse du moteur électrique permet de réduire le nombre de rapports voire de supprimer la boîte de vitesses. Il est alors possible de l'intégrer aux roues du véhicule.

L'amélioration du rendement du moteur thermique est cependant contrebalancée par les conversions mécanique/électrique puis électrique/mécanique. D'autre part, l'ensemble batterie-moteur électrique doit être dimensionné pour fournir la totalité de la puissance motrice.

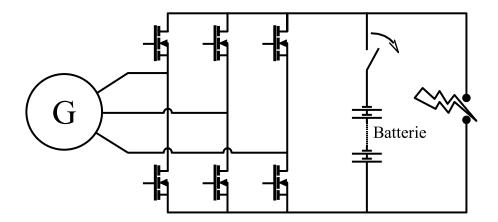

L'hybride « parallèle » visible figure 1(b) est plus proche de la structure des véhicules thermiques actuels: le moteur thermique est relié, via un embrayage et une boîte de vitesses, aux roues motrices; un moteur électrique (réversible) vient se connecter sur la liaison mécanique. On supprime ainsi les deux conversions électromécaniques de l'hybride série, et les deux machines peuvent travailler de concert pour produire une plus grande puissance. Lorsque la puissance requise est moindre, la machine électrique est utilisée en génératrice pour recharger les batteries.

Signalons enfin une troisième architecture, utilisée notamment par *Toyota*: elle fait appel à un train épicycloïdal qui remplace l'embrayage, la boîte de vitesses et effectue la liaison entre moteur thermique, moteur électrique et roues. Cette solution permet d'additionner les vitesses des moteurs thermique et électrique pour obtenir une variation continue du rapport de transmission.

#### Niveaux d'hybridation

Contrairement à l'hybridation série, dans laquelle la machine électrique doit fournir la totalité de la puissance mécanique nécessaire à la traction, l'hybridation parallèle peut se décliner en différents niveaux.

Plusieurs fonctions peuvent ainsi être assurées par la machine électrique, en fonction notamment de sa puissance [Pla01]:

Fonction stop & go Une seule machine électrique assure les fonctions d'alternateur et de démarreur. Le couplage mécanique de cette dernière avec le groupe de propulsion par une courroie (contrairement aux démarreurs classiques avec lesquels un pignon vient brièvement — et brutalement — engrener une couronne dentée) permet un démarrage du moteur thermique silencieux et rapide. Il devient ainsi possible d'effectuer des arrêts et redémarrage fréquents de ce dernier, en fait à chaque fois que le véhicule s'immobilise (feux rouges, bouchons ...).

**Freinage récupératif** Il s'agit cette fois de récupérer l'énergie cinétique du véhicule pour recharger le dispositif de stockage électrique (batterie ou con-

densateurs) au lieu de la dissiper dans les freins. Par rapport au système précédent, la gestion du stockage se complique (cyclage des batteries, surveillance de leur état de charge...).

Assistance électrique Un moteur thermique n'est que rarement utilisé à sa puissance maximale (uniquement durant les phases d'accélération). Une solution séduisante pour diminuer la consommation du véhicule est de faire appel à un moteur thermique sous-dimensionné, assisté par un autre organe mécanique pour fournir les pics de puissance: la machine électrique.

**Traction** Lorsque la puissance de la machine électrique est suffisante (supérieure à une dizaine de kilowatt environ), elle peut assurer une partie de la traction du véhicule moteur thermique éteint.

La première fonction (stop & go) peut être assurée par une machine électrique très proche d'un alternateur classique, sous une tension de bord de  $12\ V$ . Il n'y a donc que très peu de modifications à effectuer pour l'adapter à un véhicule. Au fur et à mesure que la puissance de la machine électrique augmente (pour réaliser les autres fonctions), il faut passer à une tension d'alimentation plus importante ( $42\ puis\ 300\ V$ ) et à une intégration mécanique plus complexe (au-delà de  $6\ kW$  environ, la transmission par courroie laisse la place à une intégration de la machine électrique sur l'arbre moteur). L'élément de stockage d'énergie, une simple batterie au plomb pour le stop & go, évolue lui aussi pour permettre des cycles de charge rapide (freinage récupératif) ou fournir une forte puissance (traction électrique).

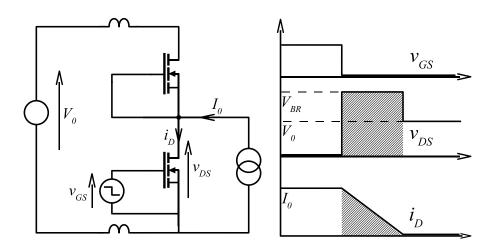

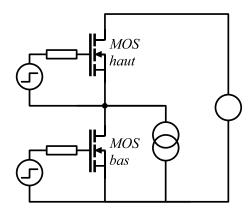

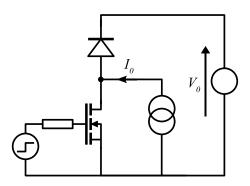

Nous nous intéresserons dans cette étude à l'électronique de puissance d'un alterno-démarreur réalisant la fonction stop & go. Il s'agit d'un onduleur triphasé, alimenté sous  $12\ V$ . Ce convertisseur réversible permet de piloter la machine électrique (fonction démarreur) ou de redresser le courant qu'elle fournit (fonction alternateur). Il faut noter que le remplacement des diodes classiquement utilisées pour la fonction redresseur par des MOSFET (dont la chute de tension à l'état passant des modèles destinées aux applications  $12\ V$  est moindre) réalise à lui seul une part non négligeable des économies de carburant de la fonction  $stop \& go \ (1 \ à 2 \ \% \ sur les 10 \ \% \ économisés au total en cycle urbain [Gau02, Pla01]).$

#### Contraintes sur l'électronique de puissance

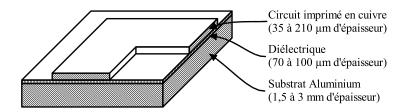

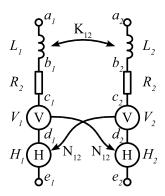

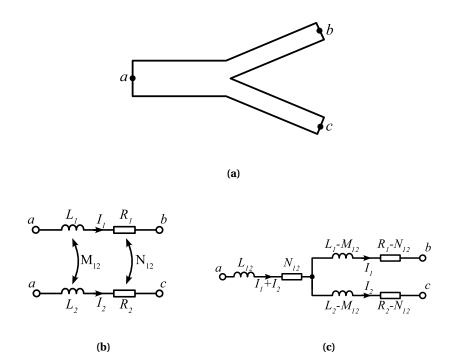

Alors que la température extérieure peut descendre jusqu'à -40 °C, la température ambiante sous le capot moteur atteint par endroits 130 °C [Kas01]. Les cyclages thermiques ainsi imposés à l'électronique s'avèrent très contraignants, d'autant que les technologies économiques utilisées en électronique de puissance y sont très sensibles : les assemblages de différents matériaux — notamment le silicium et le cuivre — de coefficients de dilatation fort différents en-

traînent des contraintes aux interfaces lors des changements de température. Ce phénomène peut mener à la casse des convertisseurs par « fatigue mécanothermique » des assemblages.

La forte valeur de la température ambiante oblige également à un surdimensionnement des convertisseurs: Peu de composants commercialisés peuvent fonctionner de manière optimale au-delà de 175 °C (notamment les semiconducteurs silicium). En considérant une température ambiante de 130 °C, il ne reste que peu de marge pour que la température de jonction des transistors ne dépasse pas la limite.

Une autre caractéristique de l'environnement automobile est sa densité en systèmes électroniques, qui pose de nombreux problèmes de compatibilité électromagnétique (CEM). On y retrouve tous les types de pollueurs : système d'allumage — qui produit des impulsions haute tension —, actionneurs électromécaniques (relais, moteurs), systèmes de forte puissance (alterno-démarreur). Les victimes potentielles sont également nombreuses : capteurs, récepteurs radio, systèmes de calcul, etc. Enfin, l'environnement extérieur est appelé à changer (le but de l'automobile est de se déplacer) et peut jouer lui aussi un grand rôle (lignes haute tension, relais téléphoniques...) Cet ensemble nécessite donc une grande attention au respect des normes CEM, qui sont d'ailleurs spécifiques à l'environnement automobile.

Si l'on ajoute les contraintes « classiques » de l'environnement automobile (tenue au brouillard salin, aux vibrations) et, bien entendu, le coût le plus faible possible, on voit que la validation d'un convertisseur réclame un grand nombre d'essais, d'autant que la fiabilité de certains organes (freinage, direction) doit être irréprochable [Fed04].

#### La simulation en électronique de puissance

Une solution pour réduire le nombre de prototypes durant la phase de conception est le recours à la simulation. Cette dernière est largement utilisée en microélectronique, où les outils permettant de la mettre en œuvre sont nombreux, mais peine à s'insérer dans le processus de conception en électronique de puissance.

Plusieurs raisons peuvent expliquer cet état de fait :

**Peu de modèles précis.** Si l'on fait exception des modèles type éléments finis (qui réclament la description complète de la structure des composants — dopage des couches et dimensions géométriques — et des temps de calcul importants), on ne trouve quasiment pas de modèles représentant fidèlement le comportement des composants de puissance, notamment en régime de forte injection [Cha98]<sup>2</sup>. De plus, même si l'on possède des

<sup>2.</sup> Il faut noter que le LAAS (toulouse), propose des modèles de nombreux composants bipo-

modèles précis, il faut procéder à l'identification de leurs paramètres avec des mesures sur les composants réels, ce qui n'est pas toujours aisé.

La raideur des simulations. L'électronique de puissance fonctionne en commutation. Les plus petites constantes de temps en simulation sont de l'ordre du pas de calcul, nécessairement faible pour décrire fidèlement les phénomènes durant la commutation (de l'ordre de la dizaine de nanosecondes). Les plus grandes constantes de temps sont au contraire liées à la durée de simulation, qui peut être très importante si l'on veut simuler des phénomènes électrothermiques par exemple (de l'ordre de plusieurs minutes). Dans un convertisseur fonctionnant à une fréquence de découpage de plusieurs kilohertz, le temps de calcul nécessaire avec un tel écart entre ces valeurs extrêmes de constantes de temps rend la simulation quasiment impossible.

**L'importance des interconnexions.** En électronique de puissance peut-être plus qu'ailleurs, les liaisons entre composants jouent un rôle primordial. Elles nécessitent donc une étape de modélisation à elles seules.

De nombreux travaux portent sur le premier point, et nous verrons qu'il est possible d'obtenir des résultats satisfaisants en combinant des modèles existants

Le second point nécessite d'adapter le type de simulation au résultat recherché: une approche CEM peut se satisfaire de quelques commutations seulement, mais avec des modèles fins. La recherche de la température en régime établi doit au contraire faire appel à des modèles simplifiés qui ne représentent pas nécessairement la commutation (modèles moyens).

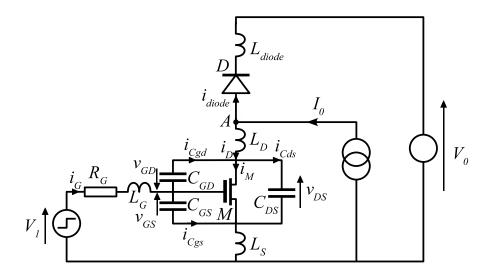

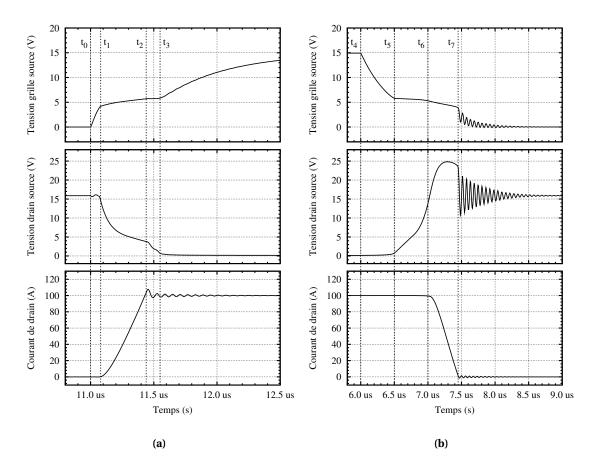

La modélisation des commutation est un élément de première importance, sur lequel portent de nombreuses études. Dans le cas des convertisseurs basse tension, fort courant, nous verrons que les effets inductifs doivent être modélisés correctement pour espérer obtenir des résultats exploitables.

#### Objectifs de l'étude

Dans ce mémoire, nous proposons une modélisation des onduleurs basse tension destinés aux applications d'alterno-démarreur. Ces convertisseurs sont alimentés sous une tension de  $12\ V$  et utilisent des transistors MOSFET comme commutateurs.

Le premier chapitre est consacré au transistor MOS. Les spécificités des composants destinés aux applications basse tension, ainsi qu'un modèle de ces transistors prenant en compte leurs différents régimes de fonctionnement sont présentés

laires de puissance [Aus03]. Dans cette étude nous ne nous intéresserons qu'à la diode PiN et utiliserons le modèle développé au CEGELY.

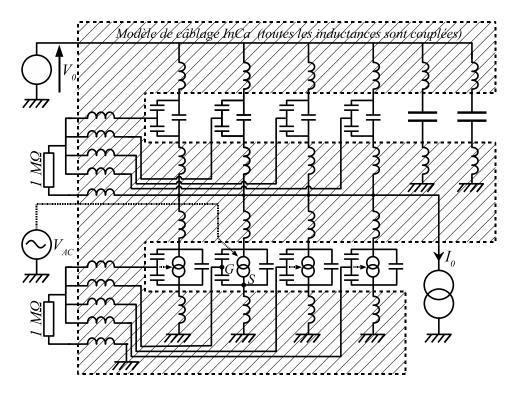

Le second chapitre démontre l'importance du câblage dans le fonctionnement d'un convertisseur. Dans un second temps, les méthodologies de modélisation de câblage que nous avons utilisées sont présentées.

Le première partie du chapitre trois regroupe la caractérisation expérimentale des modèles (c'est à dire la recherche des valeurs de leurs paramètres pour lesquelles les modèles donnent des résultats les plus proches de la mesure). Dans la seconde partie, nous validons le modèle complet du convertisseur en comparant les résultats de simulation et de mesure en faisant appel à un critère exigeant : le niveau de pertes.

Enfin, le quatrième chapitre met en œuvre les modèles obtenus pour démontrer l'intérêt de la simulation dans une démarche de conception en électronique de puissance, notamment en terme d'analyse.

## **Chapitre 1**

# Le MOSFET de puissance basse tension

Le transistor MOSFET est le composant de choix pour les applications « basse tension » : Parmi tous les composants de puissance disponibles actuellement, seul l'IGBT est aussi simple à commander, mais la chute de tension à l'état passant de ce dernier (de l'ordre de 2 V) le rend inutilisable lorsque l'on travaille avec des tensions inférieures à la centaine de volts.

Dans ce chapitre, nous décrivons le fonctionnement d'un transistor MOS-FET classique, puis les spécificités de ceux destinés aux applications basse tension. Enfin, nous proposons un modèle de ce composant de façon à pouvoir simuler son comportement.

#### 1.1 Fonctionnement des transistors MOSFET

#### 1.1.1 La structure MOS

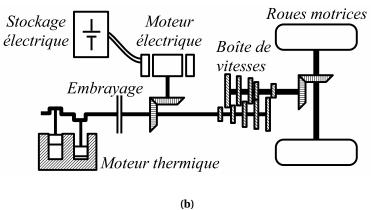

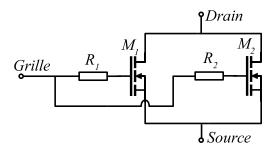

L'empilement de trois couches métallique, isolante (oxyde) et semiconductrice constitue une structure MOS (visible figure 1.1), qui est à la base du transistor éponyme.

Cette structure ressemble fortement à celle d'une capacité plane, dont l'une des armatures métalliques serait remplacée par un semiconducteur (en l'occurence du silicium dopé P). Nous allons nous intéresser à la répartition de la charge présente à la surface du semiconducteur suivant la polarisation appliquée entre G et B, car c'est elle qui conditionnera le fonctionnement du transistor.

Des charges sont présentes à l'interface entre l'oxyde et le semiconducteur, du fait de la rupture du réseau cristallin. D'autre part, la différence des travaux de sortie du métal et du semiconducteur est à l'origine d'un potentiel  $\Phi_{MS}$ . Il en résulte que pour obtenir une densité de charges en surface du silicium égale

FIG. 1.1 – Structure Métal–Oxyde–Semiconducteur

à  $q.N_A$  (la densité de charge dans le volume) il faut appliquer une tension telle que :

$$V_{GB} = V_{FB} = \Phi_{MS} - \frac{Q_0^s}{C_{ox}^s}$$

(1.1)

Où  $Q_0^s$  représente la charge d'interface oxyde–semiconducteur par unité de surface et  $C_{ox}^s$  la capacité surfacique de la couche d'oxyde. La tension ainsi obtenue est nommée  $V_{FB}$  (*Flat Band*).

Pour  $V_{GB} > V_{FB}$ , les trous sont repoussés, leur densité en surface est plus faible que dans le volume : on passe en régime de déplétion. D'après [Mas93], la charge de déplétion (par unité de surface) vaut :

$$Q_B^s = \sqrt{2\epsilon_{Si} q N_A \Phi_S} \tag{1.2}$$

$\epsilon_{Si}$  étant la permittivité du silicium et  $\Phi_S$  le potentiel le long de la zone de déplétion.

Si l'on augmente encore  $V_{GB}$ , la densité d'électrons n augmente à la surface du silicium, jusqu'a atteindre  $N_A$ : on passe en régime de faible inversion. D'après la distribution de Bolzmann, on a  $n=n_ie^{\Phi_P/U_T}$ ,  $\Phi_P$  étant la valeur de  $\Phi_S$  pour laquelle on passe en régime d'inversion. Le régime de forte inversion est atteint lorsque l'on a  $\Phi_S=2\Phi_P$  (c'est à dire une charge d'espace de même valeur que lors de la déplétion, mais de signe inverse) soit :

$$\Phi_S = 2\Phi_P = 2U_T \ln\left(\frac{N_A}{n_i}\right) \tag{1.3}$$

La tension  $V_{GB}$  lorsque  $\Phi_S = 2\Phi_P$  est appelée  $V_{th}$ . Elle représente la tension de seuil à partir de laquelle le transistor commencera à conduire, et vaut :

$$V_{th} = V_{FB} + 2\Phi_P + \frac{Q_B^s}{C_{ox}^s} \tag{1.4}$$

Soit, en remplaçant  $Q_B^s$  par sa valeur dans (1.2)

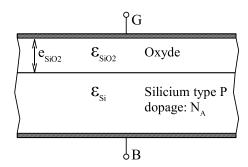

FIG. 1.2 – Principe du transistor MOSFET latéral

FIG. 1.3 – Répartition de la charge  $Q_n$  dans le canal sous l'effet d'une polarisation drain-source

$$V_{th} = V_{FB} + 2\Phi_P + \frac{\sqrt{4\epsilon_{Si} q N_A \Phi_P}}{C_{ox}^s}$$

(1.5)

#### 1.1.2 Le MOSFET latéral

Il s'agit là de la structure classiquement utilisée pour les MOSFET signal. Les trois électrodes grille, drain et source sont connectées en face supérieure (voir figure 1.2), le substrat (désigné plus loin par la lettre B, pour *Bulk*) constituant une quatrième connection.

En l'absence de tension  $V_{DS}$ , on retrouve la capacité MOS telle que décrite en 1.1.1. L'application d'une tension  $V_{GB}$  positive supérieure à  $V_{th}$  entraîne l'apparition d'un canal N dans le substrat P entre source et drain dont la résistance est donnée par [Bal96] :

$$R_{ch} = \frac{L}{W\mu_{ns}Q_n} \tag{1.6}$$

Où  $\mu_{ns}$  est la mobilité de surface des électrons, L la longueur du canal et W sa largeur (perpendiculaire au plan de la figure 1.2).  $Q_n$  est la charge disponible pour participer au courant de conduction.

Cependant, pour qu'un courant circule dans le canal, il faut appliquer une tension  $V_{DS}$ . La répartition de la charge dans le canal va être modifiée par le champ électrique ainsi exercé.

Un élément dx du canal (voir figure 1.3) est soumis à une différence de potentiel avec la grille égale à  $V_{GS} - V_c(x)$ ,  $V_c(x)$  étant le potentiel dans le canal avec

Fig. 1.4 – Pincement du canal pour une tension  $V_{DS}$  supérieure à  $V_{GS}$  –  $V_{th}$

$V_c(0) = 0$  (on a donc  $V_c(L) = V_{DS}$ ). La charge élémentaire  $dQ_n$  peut alors s'écrire :

$$dQ_n = C_{ox}^s W [V_{GS} - V_{th} - V_c(x)] dx$$

(1.7)

La résistance offerte par cet élément dx est alors :

$$dR = \frac{dx}{\mu_{ns} \frac{dQ_n}{dx}} \tag{1.8}$$

Et la chute de tension  $dV_c$  devient

$$dV_c = dR.I_D = \frac{dx}{\mu_{ns} C_{ox}^s W [V_{GS} - V_{th} - V_c(x)]} I_D$$

(1.9)

Soit, en intégrant x de 0 à L (c'est à dire  $V_c(x)$  de 0 à  $V_{DS}$ ), on obtient la valeur du courant de drain :

$$\int_{0}^{L} I_{D} dx = \int_{0}^{V_{DS}} \mu_{ns} C_{ox}^{s} W \left[ V_{GS} - V_{th} - V_{c} \right] dV_{c}$$

(1.10)

$$I_D = \frac{\mu_{ns} C_{ox}^s W}{L} \left[ (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(1.11)

L'expression (1.11) n'est valable que pour un canal continu, c'est à dire  $V_{GS}-V_{th} < V_{DS}$ . Au delà, on observe un pincement du canal du côté drain (voir figure 1.4), et le courant n'augmente plus avec  $V_{DS}$ : le MOSFET fonctionne alors en régime de saturation.  $I_D$  sature à sa valeur maximale, pour laquelle  $V_{GS}-V_{th}=V_{DS}$ . (1.11) s'écrit alors :

$$I_{D,sat} = \frac{\mu_{ns} C_{ox}^s W}{2L} (V_{GS} - V_{th})^2$$

(1.12)

Le comportement du MOSFET évolue donc avec la tension drain–source : pour les faibles valeurs de  $V_{DS}$ , le terme quadratique de l'équation (1.11) est négligeable, et on a une relation de la forme  $I_D=R(V_{GS}).V_{DS}$  (comportement purement ohmique, modulé par  $V_{GS}$ ). Lorsque  $V_{DS}$  augmente, ce terme quadratique devient de plus en plus important, jusqu'à arriver à la saturation.

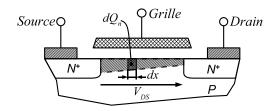

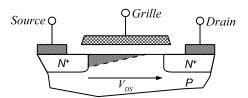

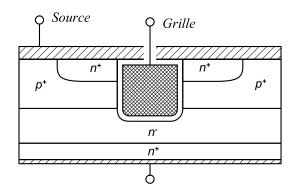

FIG. 1.5 – coupe d'une cellule de transistor VDMOS

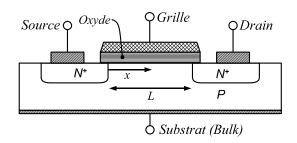

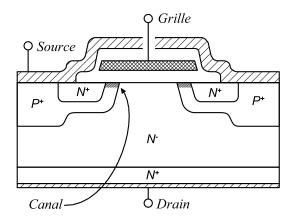

#### 1.1.3 Le MOSFET vertical

Les transistors MOSFET de puissance classiques sont obtenus par double diffusion sur un substrat épitaxié  $N^-$ , d'où le nom de VDMOS (Vertical Double Diffused MOS). Leur stucture est très proche de celle des MOSFET latéraux présentée en 1.1.2, en gardant un canal horizontal, mais en ajoutant une couche  $N^-$  dans l'épaisseur du substrat, destinée à tenir la plus grande partie de la tension drain-source lorsque le transistor est bloqué. Les contacts de drain et de source sont alors disposés de part et d'autre du substrat. La figure 1.5 présente une cellule élémentaire d'un transistor MOSFET, étant entendu qu'un de ces transistors en comporte de quelques milliers à plusieurs millions.

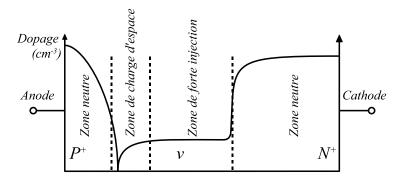

La métallisation de source, qui recouvre la face supérieure du transistor, vient relier les puits  $N^+$  de chaque cellule, mais également contacter les poches  $P^+$  pour les polariser par rapport à la grille et donc rendre le transistor commandable. Cette connexion entre source et substrat vient également court-circuiter l'émetteur et la base du transistor NPN parasite constitué des zones  $N^+_{source}$ , P et  $N^-_{drain}$ . En l'absence de ce court-circuit, une différence de potentiel entre la poche P et la source entraînerait le verrouillage du MOSFET à l'état on. L'interconnexion  $P^+ - N^+$  n'a cependant pas que des avantages : elle fait apparaître une diode entre drain et source, diode dont les performances ne peuvent être optimisées qu'au détriment de celles du transistor MOSFET (La réduction de la durée de vie, notamment, avantage les premières mais réduit les secondes). Notons tout de même que de nombreux travaux portent sur l'amélioration de cette diode.

Lorsque le MOSFET est bloqué, et en raison de la forte dissymétrie de dopage entre les zones P (canal) et  $N^-$  (couche épitaxiée), la zone de charge d'espace s'étendra en quasi totalité du côté  $N^-$ . Si l'on fait abstraction des problèmes liés à la périphérie du composant, le dopage et l'épaisseur de la couche

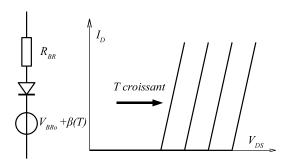

FIG. 1.6 – Localisation des différentes composantes résistives dans un MOSFET vertical

épitaxiée conditionneront donc la tenue en tension du transistor, comme toujours dans les dispositifs de l'électronique de puissance [Arn92]. Cependant, le MOSFET étant un dispositif unipolaire, aucun mécanisme de forte injection ne viendra moduler la résistivité de la couche  $N^-$  à l'état passant, résistivité elle aussi conditionnée par le dopage et l'épaisseur de la couche  $N^-$ . L'augmentation de la tenue en tension à l'état bloqué (en réduisant le dopage ou en augmentant l'épaisseur de la couche  $N^-$ ) entraîne donc l'augmentation de la résistance à l'état passant. Ce compromis  $R_{Ds_{on}}/V_{BR}$  constitue le principal inconvénient du transistor MOSFET, et le condamne aux applications *basse tension* (inférieure à quelques centaines de volts). Au dessus, l'IGBT présente en général de plus faibles pertes en conduction.

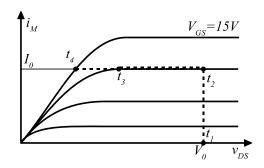

#### 1.1.4 Comportement statique

Tout comme pour le MOSFET latéral, le fonctionnement du MOSFET vertical en conduction peut être séparé en deux régimes : linéaire et saturé. Dans le premier, le courant est imposé par le circuit extérieur, le MOSFET se comportant comme une résistance modulée par la tension  $V_{GS}$ . Dans le second, le courant est limité par le transistor  $^1$ , et ne dépend plus que de  $V_{GS}$  (en première approximation).

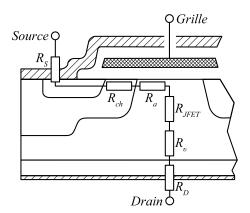

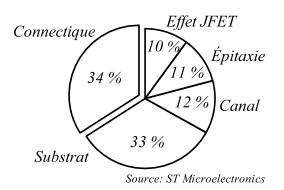

Le canal, étudié sommairement en 1.1.2 n'est plus le seul à intervenir durant la conduction dans un MOSFET vertical. On peut écrire (figure 1.6) :

$$R_{DS_{on}}(V_{GS}) = R_S + R_{ch}(V_{GS}) + R_a + R_{JFET} + R_v + R_D$$

(1.13)

<sup>1.</sup> Dans le monde du transistor bipolaire, le régime de saturation est paradoxalement celui où le transistor n'impose plus le courant...

Où:

- R<sub>S</sub> représente la résistance de source, incluant la connectique (*bondings*, métalisation, ...);

- $R_{ch}$  est la résistance du canal, modulée par  $V_{GS}$ ;

- $R_a$  est la résistance de la couche d'accumulation, située sous l'électrode de grille, dans la zone  $N^-$ ;

- R<sub>JFET</sub> représente la résistance créée par le *JFET* parasite qui apparaît entre deux cellules adjacentes;

- $R_v$  est la résistance de la couche épitaxiée;

- $R_D$  est la résistance de drain, liée à la connectique et au substrat  $N^+$ .

Certaines de ces résistances peuvent présenter une dépendance à  $V_{DS}$ , notamment  $R_{ch}$  (effet de raccourcissement du canal) et  $R_{JFET}$ .  $R_S$  et  $R_D$  ne dépendent normalement que de paramètres intrinsèques du composant, comme le dopage de ses différentes régions et sa géométrie.

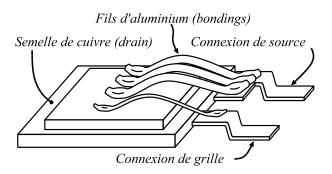

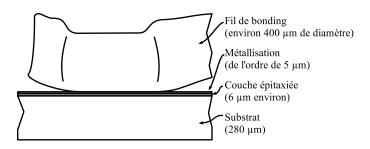

**R**<sub>S</sub> Cette résistance, souvent négligée pour les transistors haute tension (supérieure à 200V environ) constitue la majeure partie de la résistance de connectique. En effet, la puce de silicium est habituellement brasée au boîtier côté drain, alors que les connections de source se font par fils d'aluminium, ou *bondings*, plus résistifs, soudés sur une métallisation de quelques microns d'épaisseur.

${f R_D}$  Sa valeur est classiquement beaucoup plus faible que  $R_S$ , car la puce est directement brasée sur une semelle de cuivre dont l'épaisseur atteint le millimètre dans les boîtiers plastiques courants tels que le D2PAK, le TO220... Dans le cas des transistors MOSFET basse tension, fort courant, la connectique  $(R_S+R_D)$  peut être à l'origine de 50% de la résistance totale.

${f R_a}$  La conduction dans le canal se fait selon une direction horizontale (parallèle à la surface supérieure du composant). Pour rejoindre le contact de drain, au contraire, le courant va « descendre » dans l'épaisseur du composant. Ce changement de direction se fait dans la zone d'accumulation de la couche v située sous la grille (voir figure 1.7). Selon [Bal96], la valeur de  $R_a$  peut être calculée en la considérant comme une zone de silicium de mobilité  $\mu_{ns_a}$  soumise à une différence de potentiel  $V_{GS}-V_{th}$ . On introduit un facteur k (de l'ordre de 0,6) pour tenir compte de l'aspect bidimentionnel du courant . Soit :

$$R_a^s = \frac{k}{\mu_{ns_a} C_{ox}^s (V_{GS} - V_{th})}$$

(1.14)

Cette résistance augmentant avec l'espacement inter-cellulaire, on a ici tout intérêt à resserrer les cellules.

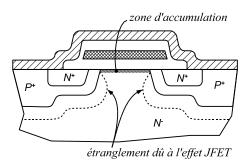

FIG. 1.7 – Mise en évidence de la zone d'accumulation et du rétrécissement de la surface active de conduction créée par le JFET parasite

${f R}_{JFET}$  Les diffusions  $P^+$  forment dans la couche  $N^-$  un transistor à effet de champ à jonction (JFET) qui va venir, sous l'effet de la tension  $V_{DS}$ — faible mais non négligeable —, moduler la section efficace de passage du courant (figure 1.7). Les besoins de tenue en tension imposant un dopage faible pour la couche  $N^-$ , la zone de charge d'espace du JFET va s'étendre rapidement [Arn92] dès que  $V_{DS}$  dépassera quelques volts :

Si l'on considère une jonction abrupte  $P^+ - N^-$  perpendiculaire à la surface du silicium, la largeur de la zone de charge d'espace peut s'écrire, de la même manière que dans l'équation 1.2 :

$$W_{JFET} = \sqrt{\frac{2V_{DS}\epsilon_{Si}}{qN_{v}}} \tag{1.15}$$

Au contraire de la résistance  $R_a$ , on ici plutôt intérêt à écarter les cellules le plus possible pour que l'effet JFET ne pénalise pas la résistance spécifique du MOS-FET.

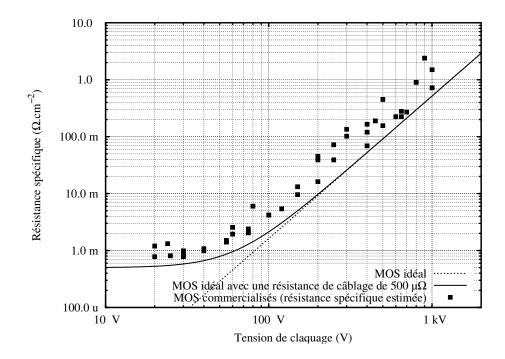

$\mathbf{R}_{v}$  Cette composante résistive est consubstantielle au principe du MOSFET. La couche épitaxiée  $(v, \text{ ou } N^{-})$  a pour rôle de tenir la tension au blocage du transistor, ce qui, en fonctionnement unipolaire, se traduit par une résistivité non négligeable. C'est par ce mécanisme que le  $R_{DS_{on}}$  des MOSFET augmente avec leur tenue en tension  $(V_{BR})$ .  $R_{v}$  constitue donc une valeur minimale théorique pour le  $R_{DS_{on}}$ . Selon [Bal96], cette valeur (surfacique) limite vaut :

$$R_{DS_{op},id\acute{e}al}^{s} = 5.93 \cdot 10^{-9} V_{BR}^{2,5} \left[\Omega \cdot cm^{-2}\right]$$

(1.16)

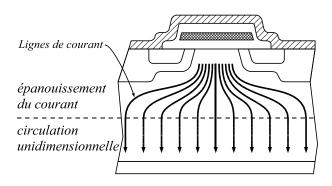

Cette formule exprime la résistance d'un bloc de silicium à dopage constant (et en considérant que la mobilité y est elle aussi constante), parcouru de façon homogène par le courant. Le resserrement des lignes de courant au au niveau de la zone cellulaire (voir figure 1.8) va encore causer l'augmentation de  $R_v$  [Mor97].

FIG. 1.8 – Épanouissement des lignes de courant au sortir de la zone cellulaire, puis circulation unidimensionelle

$\mathbf{R_{ch}}$  On retrouve dans le MOSFET vertical le canal du transistor MOSFET présenté en 1.1.2. Les expressions qui gouvernent son comportement sont donc toujours valables, notamment l'équation (1.11). Si l'on fait l'hypothèse d'une faible tension  $V_{DS}$ , valable lorsque l'on est en régime purement ohmique, le terme quadratique de (1.11) peut être négligé, et on trouve alors:

$$I_D = \frac{\mu_{ns} C_{ox}^s W}{L} (V_{GS} - V_{th}) V_{DS}$$

(1.17)

Soit:

$$R_{ch} = \frac{L}{\mu_{ns} C_{ox}^{s} W(V_{GS} - V_{th})}$$

(1.18)

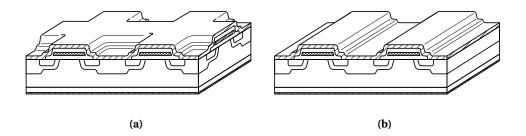

Il apparaît donc que pour réduire  $R_{ch}$ , il faut soit réduire la longueur du canal (mais il y a une valeur minimale au dessous de laquelle il y a « percement » drainsource [Mor96b]), soit augmenter la tension de commande (on a toujours intérêt à commander sous le plus fort  $V_{GS}$  possible, mais on ne peut pas dépasser 20V sans risquer d'endommager l'oxyde de grille [Arn92]), soit enfin augmenter la largeur de canal W. C'est cette dernière solution que les fabricants mettent en oeuvre en utilisant des géométries de cellules de plus en plus petites, augmentant la largeur de canal par unité de surface. On atteint de la sorte des valeurs de W de 62 m par  $cm^2$  de silicium [Bel03] (valeur donnée en 2003 pour des transistors STripfet de STMicroelectronics).

#### 1.1.5 Comportement dynamique

Le transistor MOSFET étant un dispositif à porteurs majoritaires, il ne souffre pas des lenteurs des composants bipolaires (recombinaisons, évacuation des charges...) [Arn92]. Par contre, la structure métal-oxyde-semiconducteur vue en 1.1.1 constitue une capacité, dont la charge va constituer le principal facteur ralentissant du transistor [Bal96].

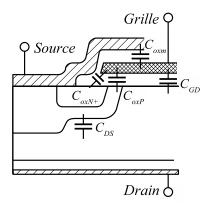

FIG. 1.9 - Effets Capacitifs

### 1.1.5.1 Capacités parasites

Si l'on considère la figure 1.9, on peut voir que la grille forme des capacités avec les différentes zones du MOSFET: entre grille et métallisation de source  $(C_{oxm})$ ; entre grille et zone  $N^+$  de source  $(C_{oxN^+})$ ; entre grille et zone P du canal  $(C_{oxP})$  et entre grille et drain  $(C_{GD})$  [Alo03]. De la même manière, lorsqu'une zone de charge d'espace se développe suivant la jonction P-N de la diode intrinsèque, une capacité  $C_{DS}$  apparaît, cette fois entre le drain et la source du transistor.

$C_{oxm}$ ,  $C_{oxP}$  et  $C_{oxN^+}$  peuvent être considérées comme des capacités constantes si l'on suppose que les zones de charge d'espace qui peuvent apparaître dans les régions  $N^+$  et P ont une épaisseur faible. Leur expression est donnée par :

$$C_{oxi} = A_i \frac{\epsilon_{ox}}{e_{ox}} \tag{1.19}$$

Où  $A_i$  est la surface en regard effective des deux armatures,  $\epsilon_{ox}$  la permittivité de l'oxyde et  $e_{ox}$  l'épaisseur de la couche d'oxyde (supposée constante tout autour de la grille).

La capacité  $C_{GD}$  a un comportement un peu plus complexe : lorsque le transitor est bloqué, une zone de charge d'espace se développe dans la région v sous l'effet d'une polarisation drain-source positive, jusqu'a l'occuper toute entière. En l'absence de cette polarisation,  $C_{GD}$  s'exprime par l'équation (1.19). Elle va donc montrer une forte sensibilité à  $V_{GD}$ . On peut la modéliser par deux capacités en série : l'une, variable, causée par l'extension de la zone de charge d'espace  $(C_{GDj})$ ; l'autre, constante, formée par la couche d'oxyde  $(C_{oxD})$

$$C_{GD} = \frac{C_{oxD} \times C_{GDj}}{C_{oxD} + C_{GDj}}$$

(1.20)

Selon [EO03], l'épaisseur de la zone de charge d'espace qui forme  $C_{GDj}$  est donnée par

$$e_{GDj} = \sqrt{\frac{2\epsilon_{Si}V_{GD}}{qN}} \tag{1.21}$$

Soit, en remplaçant  $e_{ox}$  et  $\epsilon_{ox}$  par  $e_{GDj}$  et  $\epsilon_{Si}$  dans 1.19:

$$C_{GDj} = A_{GD} \sqrt{\frac{q\epsilon_{Si}N}{2V_{GD}}}$$

(1.22)

Valable pour les tensions  $V_{GD}$  positives. En dessous,  $C_{GD}$  vaut  $C_{oxD}$ .

La capacité  $C_{DS}$  est également causée par une zone de charge d'espace, qui apparaît lorsque la jonction  $P^+ - N^-$  est polarisée en inverse. Une formulation plus poussée de cette capacité sera proposée dans la section sur la modélisation de la diode intrinsèque.

Dans l'étude qui nous intéresse, nous définirons trois capacités :  $C_{GS}$  — formée des trois capacités constantes  $C_{oxm}$ ,  $C_{oxP}$  et  $C_{oxN^+}$  —  $C_{GD}$  et  $C_{DS}$ . D'autre part, pour des raisons de facilité de mesure, on décrit parfois ces capacités sous la forme de  $C_{iss}$  (capacité d'entrée, drain et source court-circuités),  $C_{rss}$ (capacité de contre-réaction) et  $C_{oss}$  (capacité de sortie, grille et source courtcircuitées) définies, en petits signaux, par:

$$C_{iss} = C_{GD} + C_{GS} ag{1.23}$$

$$C_{rss} = C_{GD} ag{1.24}$$

$$C_{rss} = C_{GD}$$

$$C_{oss} = C_{GD} + C_{DS}$$

$$(1.24)$$

$$(1.25)$$

Pour faire commuter un MOSFET, il faut donc charger ou décharger  $C_{iss}$ , de manière à se placer sur le point de fonctionnement désiré de la caractéristique statique.

Ces capacités parasites peuvent avoir un autre effet durant les commutations:  $C_{GS}$  et  $C_{GD}$  forment un diviseur capacitif qui peut venir charger la grille du transistor lors des commutations. Autrement dit, l'application d'un gradient de tension entre drain et source peut, via le diviseur de tension capacitif, venir modifier  $V_{GS}$  et faire commuter le MOSFET de façon incontrôlée.

#### 1.1.5.2 Éléments inductifs

Le comportement dynamique du MOSFET est non seulement dicté par ses capacités(section 1.1.5.1), mais également par ses connexions au monde extérieur qui se révèlent inductives. L'assemblage d'une puce dans un boîtier de type D2PAK est visible figure 1.10. Ce type d'encapsulation est assez peu inductive (de l'ordre de la dizaine de nanohenrys entre drain et source) puisqu'il s'agit

FIG. 1.10 – Mise en évidence de la connectique interne d'un boîtier de type D2PAK (les dimensions ne sont pas à l'échelle)

là d'un Composant Monté en Surface (*CMS*) dont les pattes sont courtes. Malgré tout, lors de commutations, les fortes vitesses de variation du de courant que supporte le circuit drain-source sont à l'origine de ddp non négligeables (de quelques centaines de millivolts à quelques volts), réparties notamment sur les *bondings*. Le circuit de grille, référencé par rapport à la source, subit donc aussi cette ddp, qui agit comme une contre-réaction sur la commande, et peut être à l'origine d'instabilités lors des commutations [Mer96].

#### 1.1.5.3 Diode intrinsèque

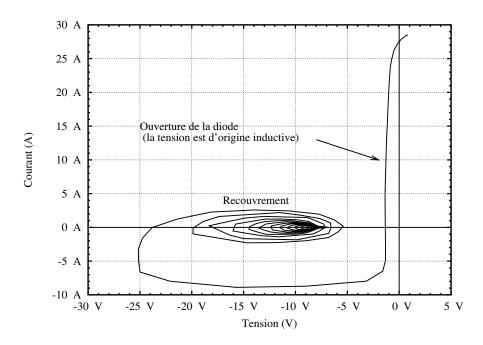

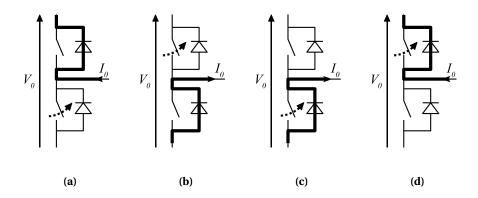

La capacité  $C_{DS}$  présentée dans la figure 1.9 est la capacité de jonction de la diode intrinsèque. Cette diode, dont la présence est inévitable sous peine de se retrouver avec un transistor NPN parasite totalement incontrôlable, a long-temps été considérée comme inutilisable, et des schémas ont été proposés pour s'en affranchir [Arn92].

La situation s'est nettement améliorée, et des méthodes ont été développées pour réduire la charge recouvrée lors des commutations. C'était nécessaire, car dans des applications de type onduleur, la diode intrinsèque est un composant fonctionnel à part entière [Bud97]. L'irradiation électronique permet de réduire la durée de vie des porteurs par un facteur de plus de trois [Bal96], au point que les diodes intrinsèques des MOSFET peuvent rivaliser avec des diodes PiN discrètes.

D'autres méthodes permettent d'augmenter la rapidité de la diode intrinsèque, comme un dopage d'or ou de platine. Ces solutions ont cependant un effet négatif sur le  $R_{DS_{on}}$  [Arn92, Bal96] car elles réduisent la mobilité dans le canal

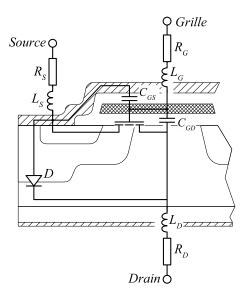

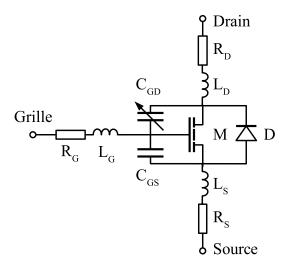

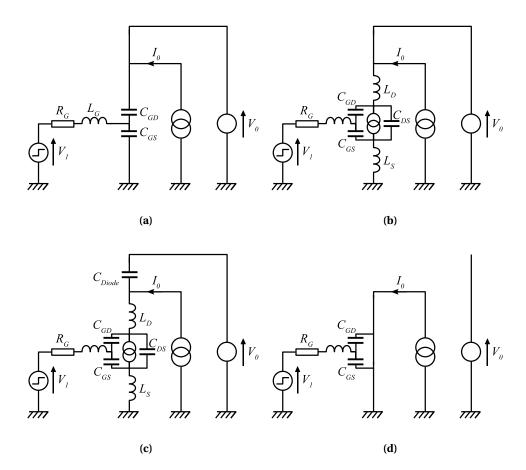

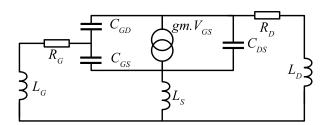

Les éléments participant au comportement dynamique du MOSFET de puissance sont repris schématiquement sur la figure 1.11.

FIG. 1.11 – Modélisation à l'aide d'éléments discrets du comportement dynamique du transistor MOSFET)

# 1.2 Spécificités des applications basse tension, fort courant

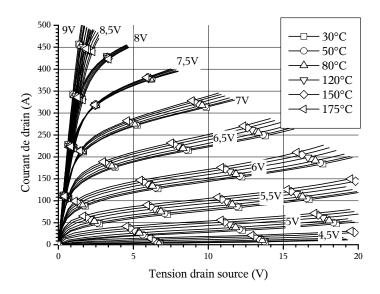

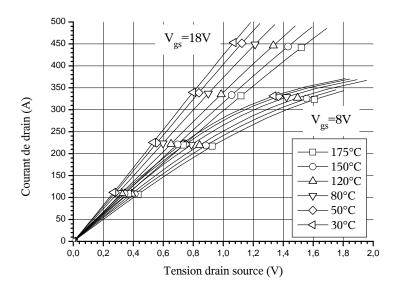

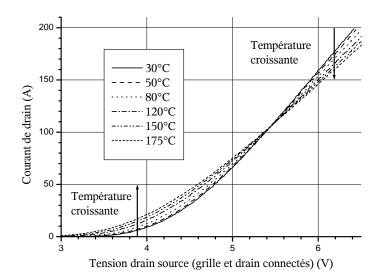

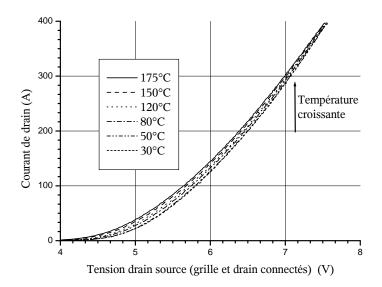

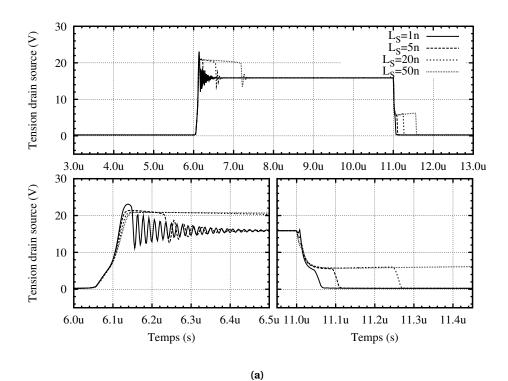

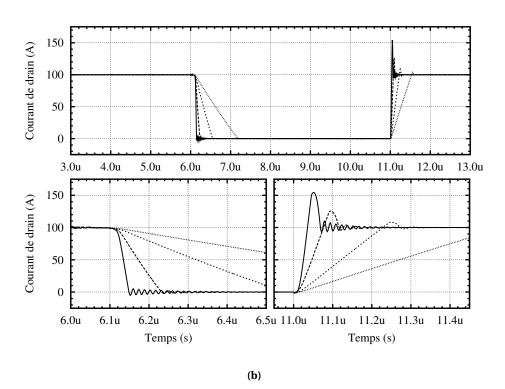

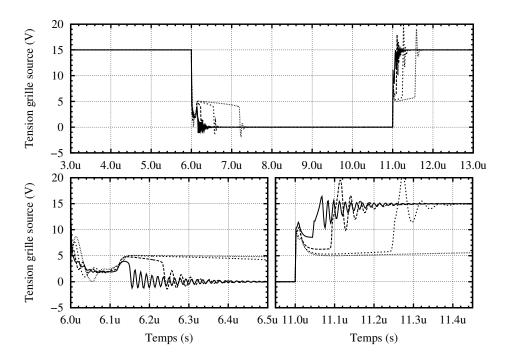

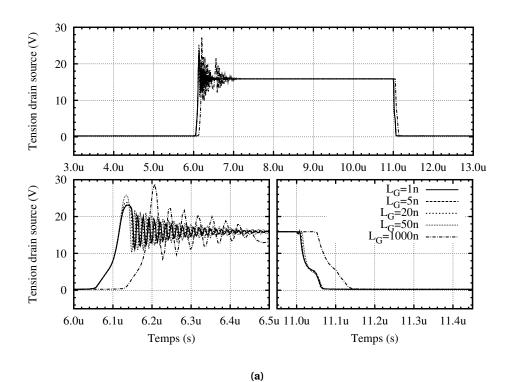

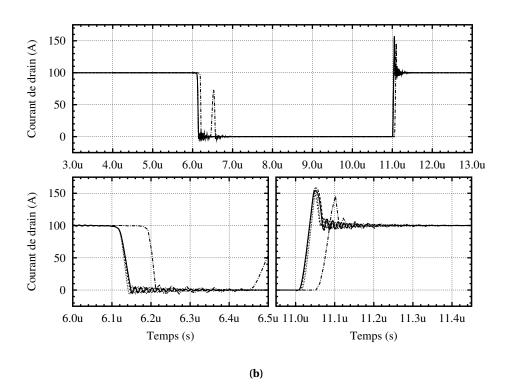

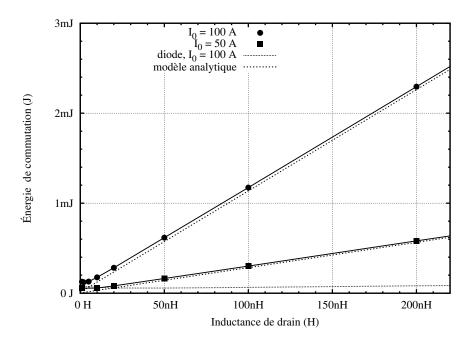

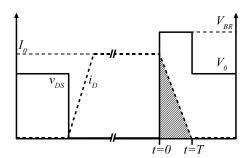

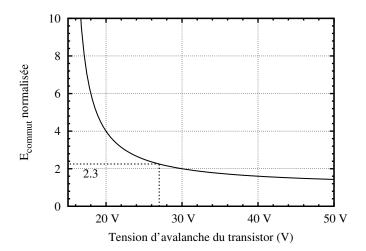

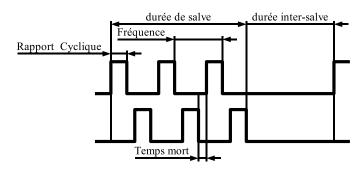

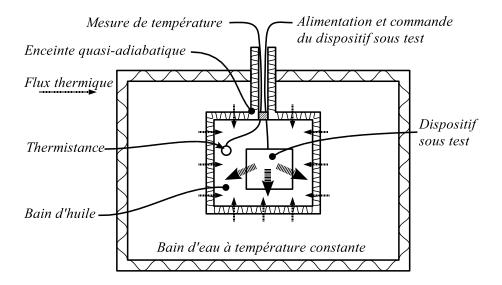

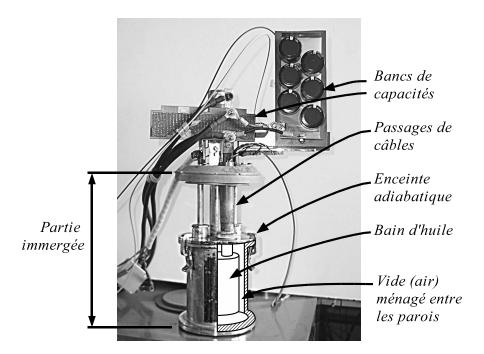

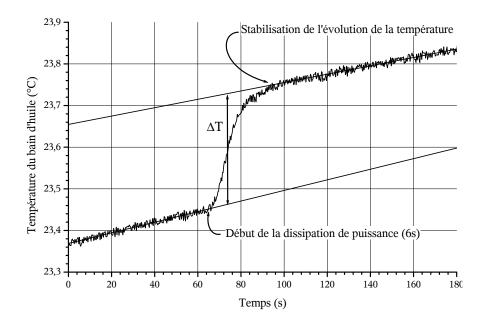

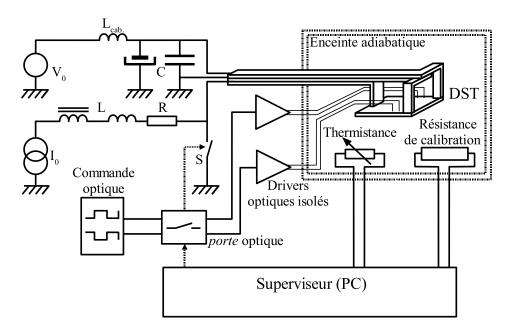

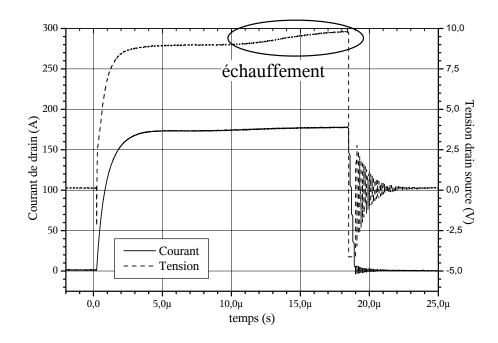

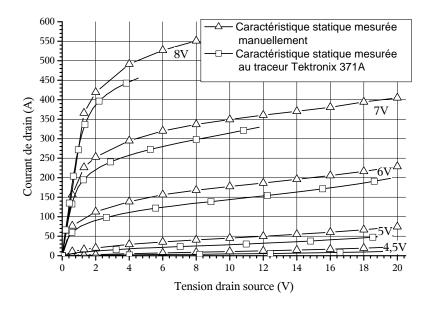

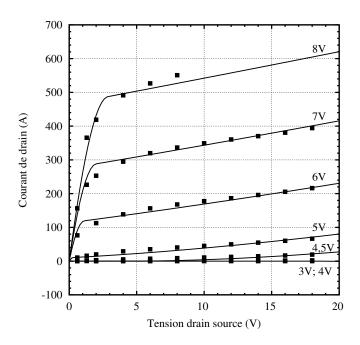

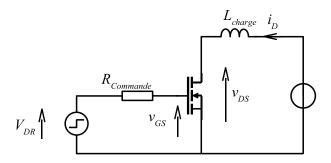

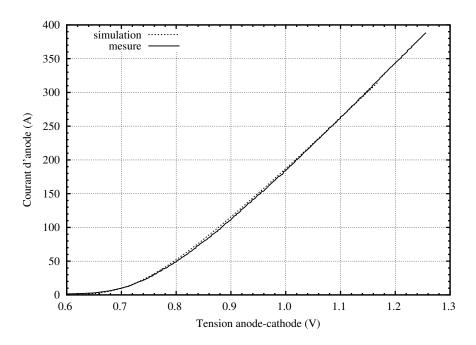

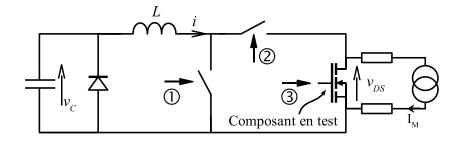

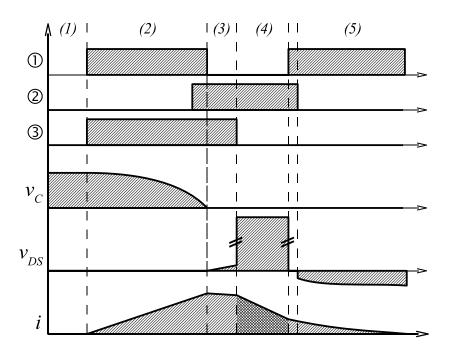

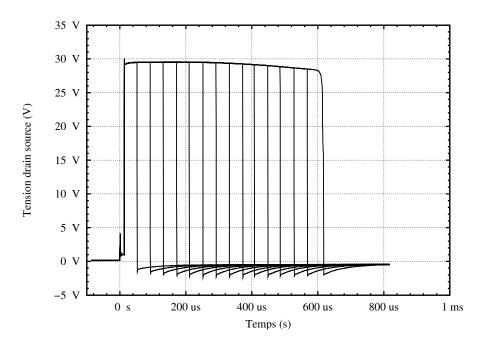

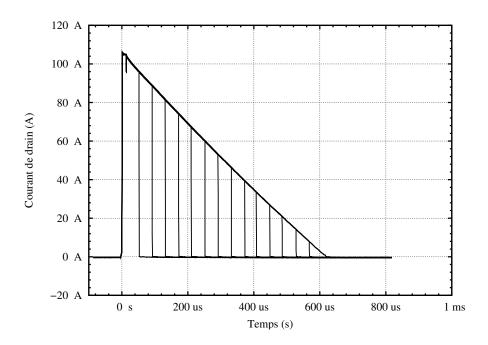

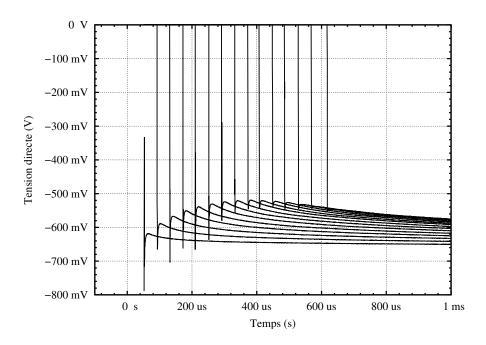

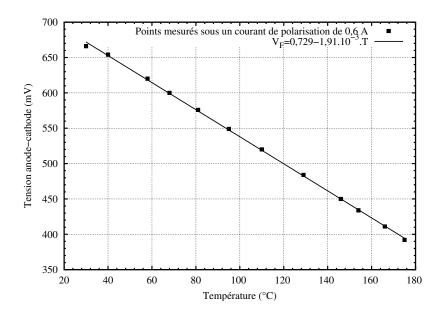

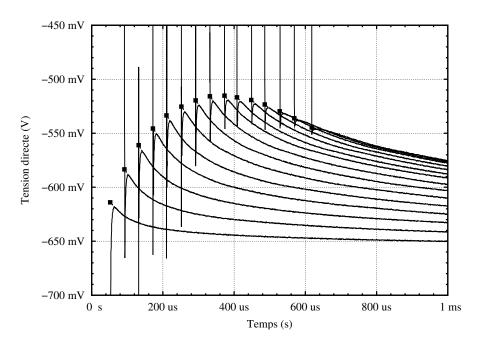

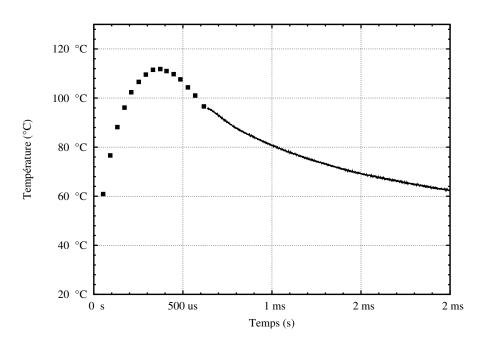

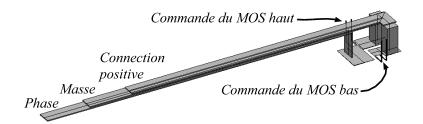

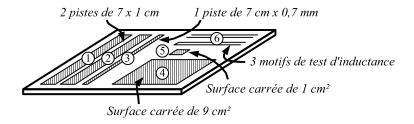

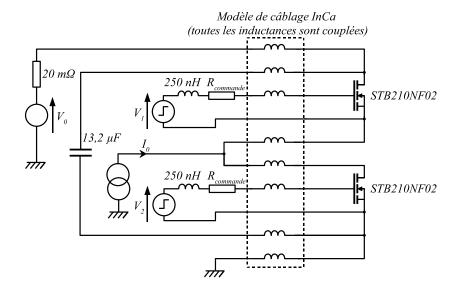

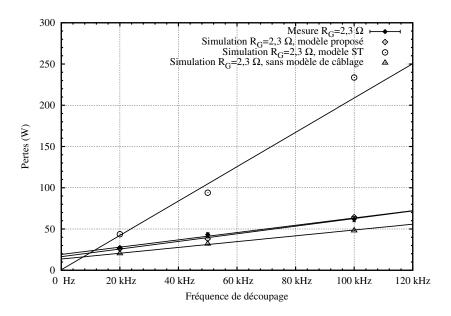

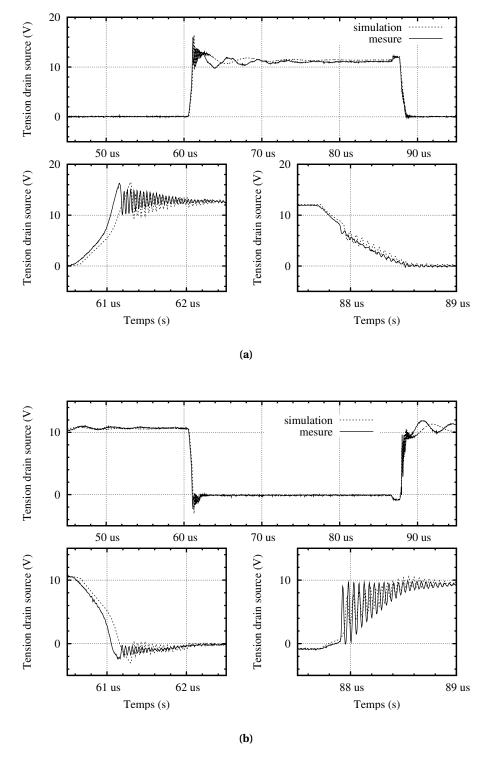

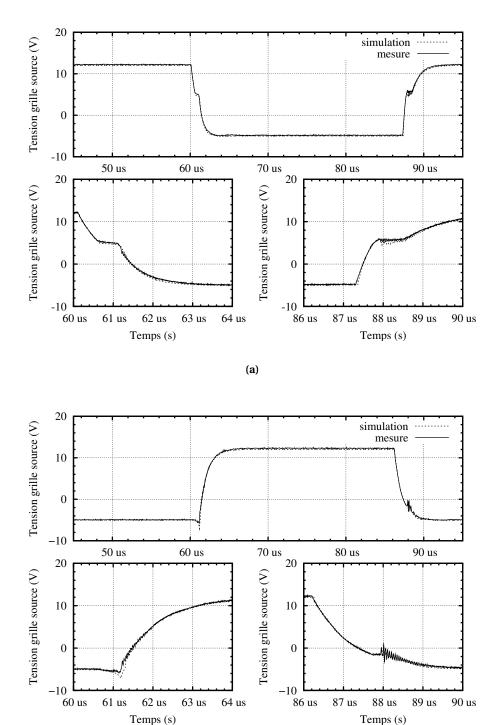

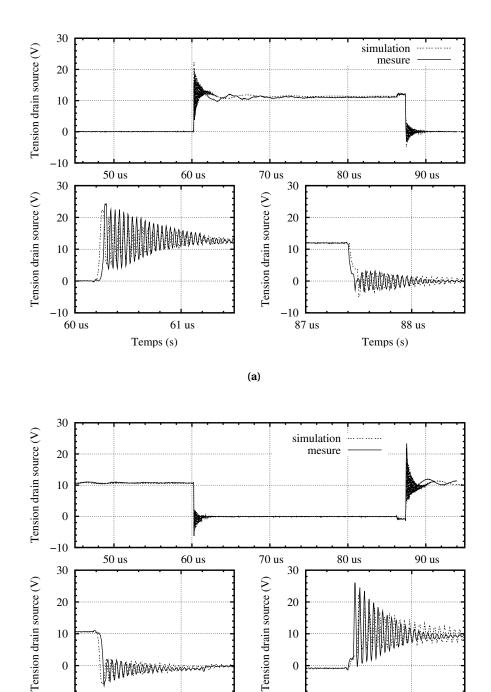

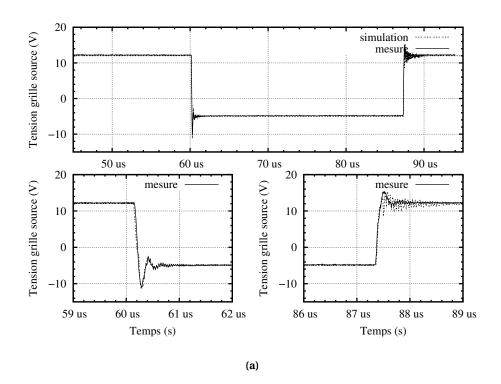

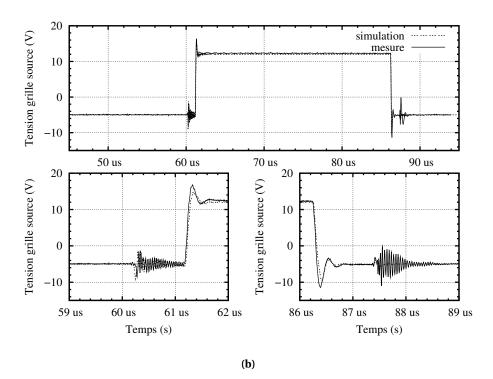

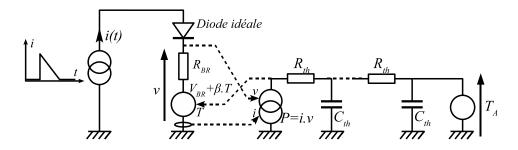

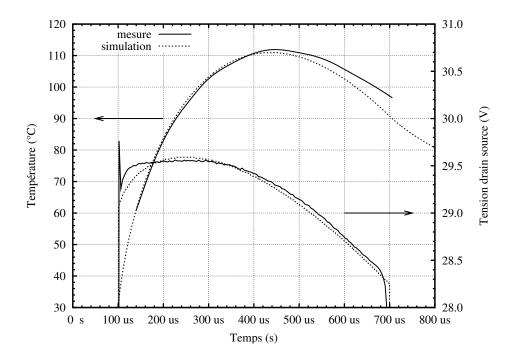

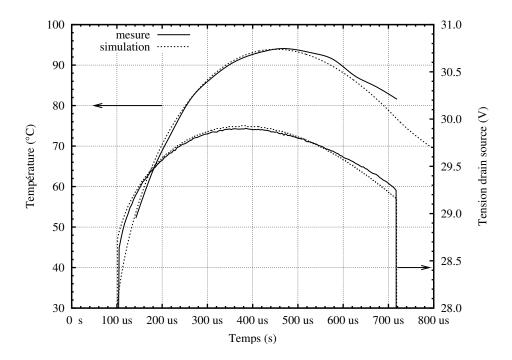

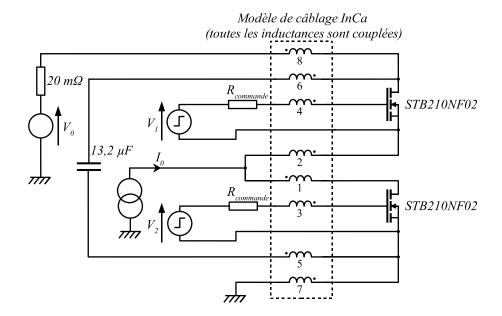

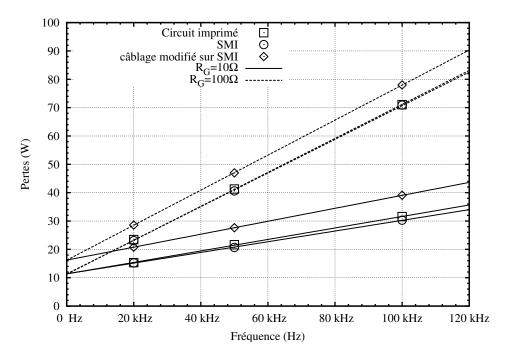

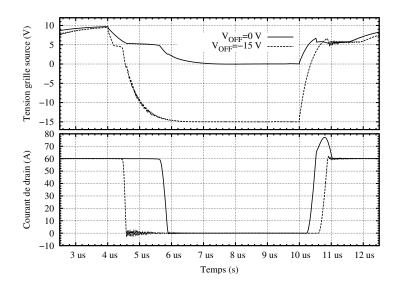

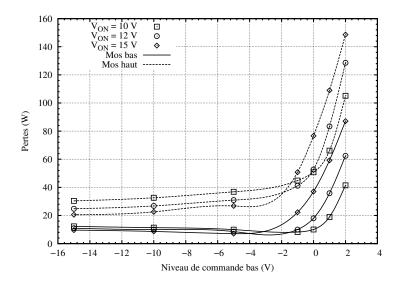

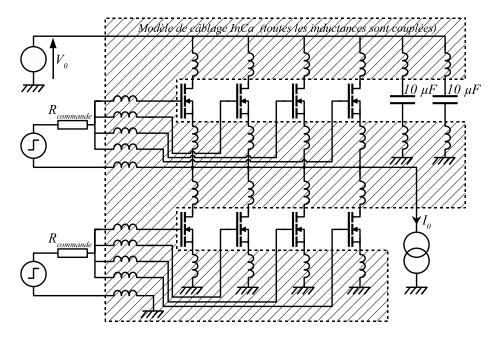

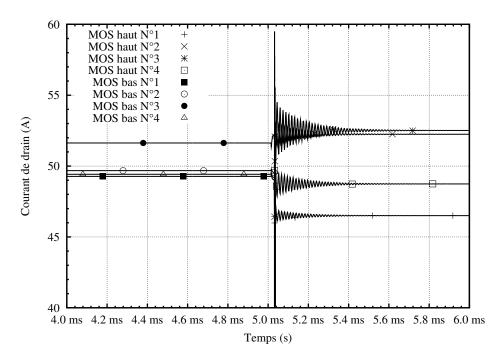

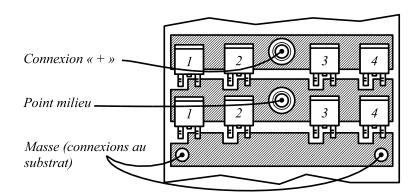

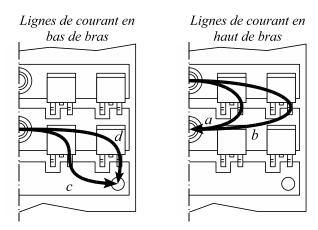

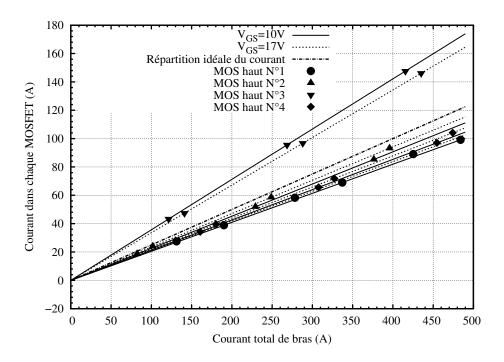

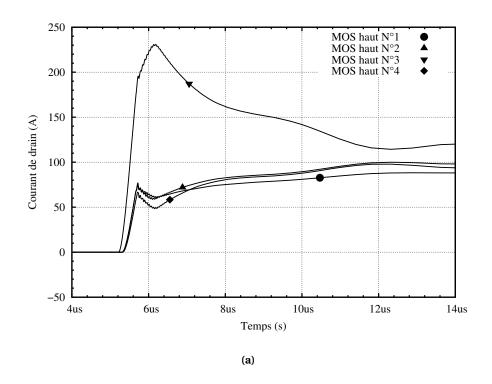

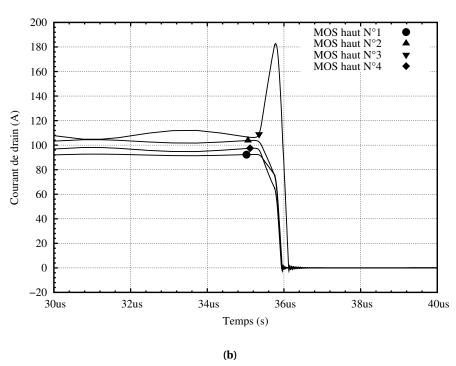

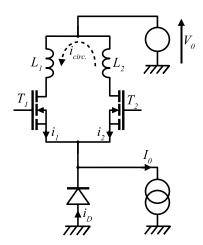

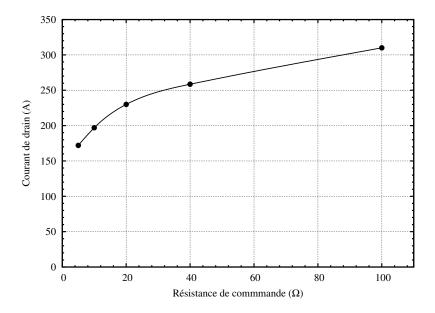

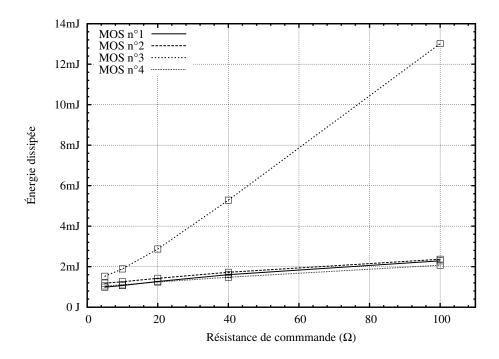

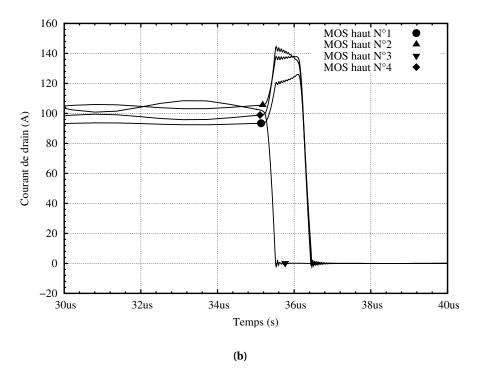

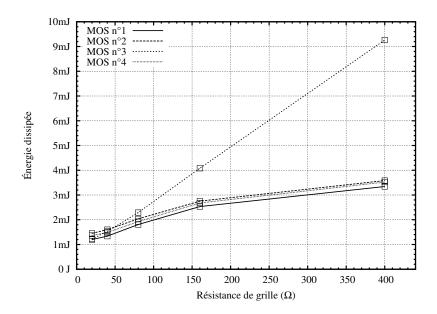

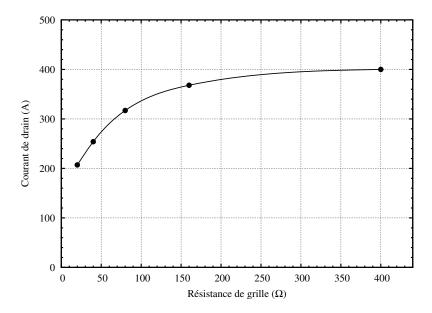

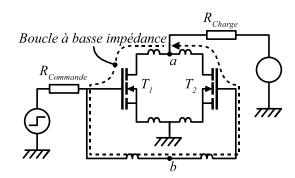

L'étude présentée ici porte sur les MOSFET de puissance destinés aux applications automobiles. Ils se caractérisent par une faible tenue en tension (typiquement 25 V pour une utilisation sur batterie 12 V et 55 V ou 75 V pour le réseau 42V), qui leur autorise un faible  $R_{DS_{on}}$ . En raison de la faible tension de travail, les courants mis en jeu vont rapidement devenir importants dès que la puissance commandée atteindra le kilowatt.